Sistema de hardware reconfigurable para aplicaciones de control

Reconfigurable hardware system for control applications

Javier Ernesto Santos Estepa

Aldemar Fonseca Velásquez

Artículo de investigación

#### Sistema de hardware reconfigurable para aplicaciones de control

### Reconfigurable hardware system for control applications

Javier Ernesto Santos Estepa <sup>1</sup>

Licenciado en Ingeniería de control, *Universidad Distrital Francisco José de Caldas, Bogotá,*Colombia

Jvrsnts13@gmail.com

Aldemar Fonseca Velásquez <sup>2</sup>

Licenciado en Ingeniería electrónica, *Universidad Distrital Francisco José de Caldas;* Maestría en Ciencias de la ingeniería, *Universidad Nacional de Colombia, Bogotá, Colombia*<a href="mailto:afonseca@udistrital.edu.co">afonseca@udistrital.edu.co</a>.

#### Resumen

Actualmente, los sistemas basados en hardware reconfigurable que se desarrollan para aplicaciones específicas se conocen como sistemas embebidos -SE-; estos sistemas analizan o controlan generalmente un proceso que ha sido parametrizado y configurado para una respuesta específica y, en dependencia de la calidad de reconfiguración mencionada, pueden

aplicarse o adaptarse a otro nuevo o algún proceso existente, de manera eficaz. El artículo describe la investigación que plantea un hardware soportado en una estructura básica reconfigurable, con la posibilidad de resultados variables por medio de la modificación de parámetros preestablecidos por software. El SE, enfocado específicamente al control de nivel de líquidos permite la simulación y la reprogramación de módulos análogos y digitales

BSc. In Control Engineering, Universidad Distrital Francisco José de Caldas, Colombia. Current position: Ericsson de Colombia, Colombia. E-mail: jvrsnts31@gmail.com. ORCID:https://orcid.org/0000-0002-5920-4281

BSc. In Electronic Engineering, Universidad Distrital Francisco José de Caldas, Colombia; MSc. Engineering Sciences, Universidad Nacional de Colombia, Colombia. Current position: Professor, Universidad Distrital Francisco José de Caldas, Colombia. E-mail: afonseca@udistrital.edu.co. ORCID: https://orcid.org/0000-0002-7904-4676

de un hardware basado en la lógica de un control de lazo cerrado, habilitando una gama de posibilidades con la combinación de cada uno de los módulos de un microcontrolador CY8CKIT-059 PSoC® 5LP. La implementación, realizada en una planta AMATROL T5552, tuvo en cuenta los voltajes y corrientes adecuados, por lo que los resultados -adicionando acoples y protecciones - son visualizados en una interfaz gráfica mediante pruebas sobre la planta de manera confiable.

*Palabras clave:* sistema embebido, hardware reconfigurable, aplicaciones de control, control de lazo cerrado, CY8CKIT-059 PSoC® 5LP, AMATROL T5552.

#### Abstract

Currently reconfigurable hardware-based system developed for specific applications are known as embedded system (ES); in general, this system analyses or control a single process and, depending on the mentioned reconfiguration quality, they can be applied or adapted to a new one or some existing process, efficiently. The article describes the investigation that raises a supported hardware in a reconfigurable basic structure, with the possibility of variable results through the modification of pre-established

parameters by software. The ES, specifically focused on a liquid level control, allows the simulation and reprogramming of analog and digital hardware modules based on the logic of a closed-loop control, allowing a range of possibilities with the combination of each one of the modules of microcontroller CY8CKIT-059 PSoC® 5LP. The implementation, carried out in an AMATROL T5552 plant, considered the appropriate voltages and currents; therefore, the results, adding couplings and protections, are displayed in a graphical interface by means of tests in the plant, without controllers, in a reliable way.

*Keywords:* embedded system, reconfigurable hardware, control applications, closed-loop control, CY8CKIT-059 PSoC® 5LP, AMATROL T5552.

#### 1. Introducción

Actualmente, los sistemas basados en hardware reconfigurable que se desarrollan para aplicaciones específicas se conocen como sistemas embebidos —SE-; estos analizan o controlan generalmente un solo proceso que ha sido previamente parametrizado y configurado.

En la literatura se han reportado variadas investigaciones sobre SE (Pérez, et al., 2018;

Enríquez, et al., 2018; Saavedra, 2008; Romero et al., 2015; Moroz et al., 2012), específicamente orientadas a diseños e implementaciones de detección de movimiento, prototipos basados en FPGA para adquisición de datos sísmicos, procesamiento de señales en desempeño de operación, control y supervisión de tráfico vehicular, o caracterización de sistemas operativos en tiempo real.

Ahora, desde el punto de vista de la representación y teniendo en cuenta los simuladores como herramientas de depuración que permiten mediante software acercarse al funcionamiento de SE basados en Simulink de Matlab®, y PSoC (Palacios y López, 2006; Dominguez, et al., 2010; Gómez-Almadana 2002; Jiménez Núñez y Panchi Campos, 2011; Nuaymi, 2007; Marzo y Estrada, 2011), las aplicaciones están orientadas a: digitalización de señales en System Generator de Xilinx, creación de interfaces de usuario para radares, modulador y demodulador N-QUAM, o aplicaciones sobre Spartan 3E-Starter.

Por otro lado, para el diseño de SE (Cabrera-López y Velasco-Medina, 2011; Cabaiguan, 2017; Espinar, 2011; Borges y Montaña, 2011; Argote-Fuertes, 2011; Guerrero, 2017; Cabrera-López, 2007; Martínez et al., 2010; Montoya et al., 2011; Bas Gago, 2010; Delgadillo, et al.,

2009; Custodio, 1999; Morales et al., 2014; Vergara-González y Estrada, 2008; Jiménez, et al., 2015; Urbina y Martínez, 2012; Vergara y Estrada, 2008; Mota, 2008; Espinosa, 2012; Gutierrez et al., 2006; y Ogata, 2018); las implementaciones se han orientado al de señales procesamiento ultrasónicas. desarrollo de microcontroladores integrando bloques análogos y digitales, emuladores fotovoltaicos para el testeo de inversores, Embedded IDE Link para implementar código en microcontroladores, control adaptativo y bioinspirado de procesos de laboratorio de automática, uso de FPAA y bloques análogos en filtros. implementación de filtros FIR. optimización de sistemas reconfigurables en anemómetros ultrasónicos, emuladores comunicación de microcontroladores PIC 16F84 basados en FPGA, uso de FPAA para aproximar inteligentes reconfigurables, sensores V monitoreo y comunicación de temperatura a profundidad marina, simuladores de modulación y demodulación OFDM, diseño y análisis de sistemas de comunicaciones de banda ancha inalámbricos, interfaces de usuario en la implementación de electro miógrafos, evaluación bioinspirada de movimiento en tiempo real, y, particularmente interesante resultan las aplicaciones biomédicas con el fin de optimizar el diseño, adquisición, conversión y análisis de datos de calibración en el nivel de cargas dentro de un encaje protésico para amputaciones a nivel transfemoral integrando herramientas como Solid Edge®, Algor®, LabView®, y SimiMotion® para simular el comportamiento de las fuerzas involucradas en el interior del encaje protésico; entre muchas otras que siguen apareciendo en los ambientes industriales y académicos.

De otro lado, extender los SE a disímiles entornos de tarea específicos (Nieto et al., 2017; Salamanca, 2018; Caicedo y Smida, 2016; Duarte y Borrás, 2016; Montiel et al. 2016; Briñez de León et al. 2017; García et al., 2016; Herrera-Cubides et al., 2019; y Angulo et al., 2017), específicamente orientados geolocalización, monitorización de signos vitales, demandas de los sistemas de salud, robótica paralela, optimización de antenas, resolución de imágenes, complejidad biológica, el Data, o el almacenamiento de energía, son desafíos vigentes en investigación, desarrollo e implementación de tecnología e ingeniería electrónica de SE.

De acuerdo con los anteriores antecedentes, el problema de SE basados en la teoría de control de lazo cerrado, y hacia una aplicación directa del diseño en una planta de control de nivel de líquidos, ha sido abordado realizando

modificaciones al diseño original en componentes físicos lo cual ha generado alto riesgo de daño. Es por ello que la presente investigación plantea una solución con un hardware soportado en una estructura básica reconfigurable, teniendo la posibilidad resultados variables por medio de la. modificación de parámetros preestablecidos por software. En consecuencia, el presente artículo reporta la investigación que condujo al desarrollo e implementación de un SE enfocado específicamente al control de nivel de líquidos, desarrollando un software que permite la simulación y la reprogramación de los módulos análogos y digitales de un hardware basado en la lógica de un control de lazo cerrado.

El artículo se estructura de la siguiente manera: se establecen los materiales y métodos para la implementación con las características de un control en lazo cerrado; posteriormente, se diseña e implementa el prototipo experimental: interfaz gráfica, algoritmo de reprogramación de bloques, estructura de hardware básica para reconfiguración de bloques, y aplicación en la planta de nivel AMATROL T5552; a continuación, se realizan las pruebas sobre la planta -sin calcular controladores- y se obtienen los resultados; finalmente se establecen las conclusiones.

### 2. Materiales y Métodos

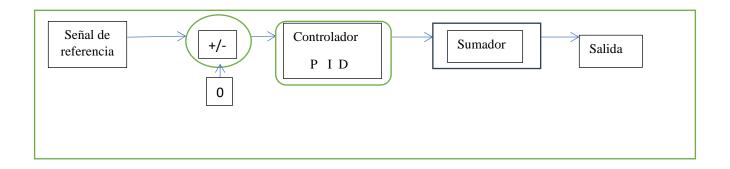

Para modificar los bloques y parámetros del microcontrolador, además de obtener resultados en tiempo real sin la necesidad de realizar modificaciones físicas a componentes, se implementa una interfaz gráfica en el entorno de desarrollo MatLab® con la posibilidad de realizar, además, una simulación sobre el estado del proceso. El sistema, por tanto, posee las características presentadas por un diagrama de bloques en un control de lazo cerrado: la salida C(s) se realimenta al punto de suma, donde se compara con la entrada de referencia R(s). La salida del bloque, C(s) en este caso, se obtiene multiplicando la función de transferencia G(s) por la entrada al bloque, E(s). Cualquier sistema de control lineal puede representarse mediante un diagrama de bloques formado por puntos de suma, bloques y puntos de ramificación.

Una vez se establece el entorno de programación y las características para la simulación y

programación del hardware, se implementa el diseño en un microcontrolador CY8CKIT-059 PSoC® 5LP. Este cuenta con la posibilidad de permitir la modificación de los módulos análogos y digitales internos; también, por la tecnología ARM implícita en su fabricación, permite que se reconfigure internamente sin la necesidad de desmontarlo del sistema implementado a través de una interfaz gráfica que verifica no solo la información técnica de lo que se está modificando en el sistema de hardware; permite visualizar además el tipo de sistema a obtener con dichos parámetros. Por tanto, se implementa el sistema en la planta de nivel de líquidos AMATROL T5552. Teniendo en cuenta que los voltajes y corrientes de la planta son altos, se diseñan acoples y protecciones para evitar daños bien sea en el PC donde se implementa la interfaz gráfica o en el microcontrolador. La tabla 1 describe las etapas metodológicas del sistema.

Tabla 1

Etapas para el desarrollo del sistema reconfigurable.

| Etapa | Siguiente etapa | Resultado |

|-------|-----------------|-----------|

|       |                 |           |

| Conocimiento de la planta<br>donde se implementa el<br>sistema                    | Aplicación en la planta de nivel                                                     | Se estudian y documentan todos los sensores y actuadores que posee la planta, y las debidas precauciones que se deben tener                                                                                                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Se establece la mejor opción de interfaz gráfica                                  | Desarrollo interfaz<br>gráfica                                                       | durante su manejo.  Se establece que la mejor opción para la interfaz gráfica es una que muestre los cambios hechos al hardware, además de                                                                                                                                                                                                                                  |  |  |

| de interiaz granea                                                                | granea                                                                               | modificar los parámetros de cualquier PSoC, según lo requiera el usuario.                                                                                                                                                                                                                                                                                                   |  |  |

| Se estudia el mejor PSoC para el sistema                                          | Estructura de hardware<br>básica que permita la<br>reconfiguración de sus<br>bloques | En coherencia con los planteamientos hechos en el inicio del sistema, donde se sabe que la tecnología de PSoC tiene posibilidades análogas y digitales, se establece que la actualización del entorno de programación PSoC, además de la llegada de una nueva gama de microcontroladores como es el caso del PSoC 5LP, permitirá el desarrollo completo de todo el sistema. |  |  |

| Desarrollo interfaz grafica                                                       |                                                                                      | La interfaz gráfica se desarrolla en MatLab, ya que sus toolbox, permiten no solo la conexión con otras plataformas, sino también la implementación de una interfaz gráfica que controle todo e informe del proceso.                                                                                                                                                        |  |  |

| Algoritmo de reprogramación de bloques                                            |                                                                                      | El desarrollo del algoritmo de reprogramación de los bloques estará dividido en dos partes, una de las cuales estará en la interfaz gráfica y la otra en el microcontrolador.                                                                                                                                                                                               |  |  |

| Estructura de hardware básica<br>que permita la reconfiguración<br>de sus bloques |                                                                                      | La estructura que se estableció y que se seguirá en todo el sistema es la de lazo de control cerrado, el cual se diseña e implementa para verificar su funcionamiento.                                                                                                                                                                                                      |  |  |

| Aplicación en la planta de nivel                                                  |                                                                                      | La aplicación en la planta de nivel deberá ser de manera continua y que pueda establecerse qué rangos de trabajo tiene la planta cuando se desarrolla algún tipo de comunicación y reprogramación de parámetros.                                                                                                                                                            |  |  |

Por otra parte, la interfaz gráfica junto con la simulación tiene por objetivo predecir resultados

de alguna combinación de la plantilla desarrollada. Permite reprogramar los módulos

del microcontrolador PSoC, sin la necesidad de ir a la plataforma de programación PSoC creator. Por esta razón, se establece una plantilla predefinida y se usan dos microcontroladores PSoC: supuestos los resultados duplicados, se programan cualquiera de los dos sin la necesidad de que el usuario modifique parámetros de manera física, sino que la interfaz permite la reprogramación de cualquiera de los módulos en alguno de los PSoC. Como se está en el caso de microcontrolador, con voltajes de alimentación entre 3,3v 5v, no podrá esperarse salidas de voltaje superiores a los voltajes de alimentación. Teniéndose en cuenta que el código que se genera, tanto en MatLab® como en PSoC, debe tener alguna manera de comunicarse y de interactuar; inicialmente se plantea usar un protocolo USB -puesto que el microcontrolador y el PC tienen estos puertos- pero se define el protocolo RS232 por efectos de compatibilidad de desarrollo en PSoC.

Teniéndose la aplicación práctica en una plataforma, se establece un lazo de control que permite la realimentación de valores y la modificación de otros. Se escoge la planta de líquidos *AMATROL* por la variedad sensores y la

disposición de tanques interconectados - cada uno con un nivel diferente- y dos sensores de nivel: uno de presión hidrostática y otro ultrasónico, y una válvula de control proporcional.

En el presente artículo, sin embargo, no se exhiben los cálculos desarrollados para escoger los diferentes componentes para obtener los modos de control deseados, los cuales se obtienen de la configuración de los modos de control en amplificadores operacionales, más bien se centra sobre la puesta en marcha de la planta de nivel probando y tabulando todos los datos obtenidos cuando la planta está en funcionamiento, estableciéndose parámetros sobre: válvula de control proporcional, sensor de nivel ultrasónico, sensor de nivel de presión diferencial, válvulas de apertura de líquido y tanques de la planta. Prueba con la planta sin controladores.

# 3. Implementación prototipo experimental3.1. Desarrollo de la interfaz gráfica y

simulación de la estructura básica

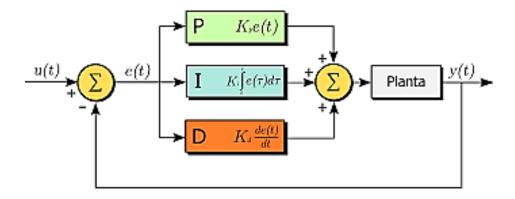

Se establece que el lazo de control tradicional (figura1), en el cual se utilizan: 1 restador, 1 bloque proporcional (P), 1 bloque integral (I), 1 bloque derivativo (D), 1 bloque de suma es la estructura básica, a realizar desde la interfaz hasta la aplicación en forma de hardware.

Figura 1: Modelo de lazo de control paralelo.

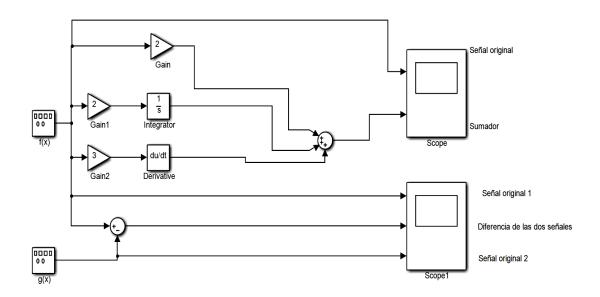

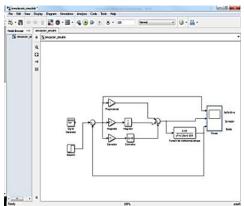

Para lo anterior se desarrolla una estructura básica en Simulink® (figura 2), que permite visualizar los posibles resultados del hardware frente a entradas de diverso tipo.

Esta estructura básica de Simulink® será controlada por la interfaz gráfica desarrollada en GUI, de tal manera que se puedan variar los parámetros desde allí.

Figura 2: Estructura básica implementada en Simulink®.

Fuente: Elaboración propia.

La interfaz gráfica cumplirá dos funciones esenciales: reprogramación de los bloques de los microcontroladores, y la generación de una simulación que permita visualizar qué resultados se pueden obtener con los valores establecidos anteriormente.

# 3.2. Desarrollo del algoritmo de programación del microcontrolador

Debido a que se pretende la reprogramación de los bloques de PSoC desde una interfaz gráfica que pueda generar además una simulación, el algoritmo encargado de esa tarea tendrá como finalidad la comunicación de MatLab® con los microcontroladores. Se opta por usar un protocolo de comunicación compatible con PSoC y Matlab serial RS232, con el cual MatLab® solo necesita de 4 líneas de código (figura 3), para realizar la comunicación y la reconfiguración de los módulos de PSoC.

```

s1=serial('COM10','BaudRate',115200,'Parity','none','DataBits',8,'StopBits',1);

fopen(s1);

fprintf(s1,'D');

fclose(s1);

```

Figura 3: Líneas de código básicas para envío de datos desde MatLab® a los microcontroladores.

Fuente: Elaboración propia.

La primera prueba del protocolo se realiza con el software Hércules, que demuestra que los datos enviados desde MatLab® son compatibles con el protocolo de comunicación, y que, además, permite el envío de datos hacia PSoC.

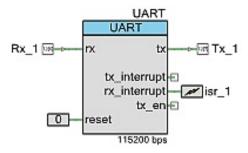

El algoritmo de programación se divide en dos partes: una que se encuentra en el código de MatLab® que envía los datos que el usuario desea reprogramar y la otra en PSoC donde se recibirán los datos y se modificarán los bloques que se requieran; también en PSoC se utiliza un bloque específico para la comunicación donde se configuran los parámetros procedentes del código.

Figura 4: Bloque UART configurado a 115.200 bps, velocidad que también se configura en MatLab®.

Fuente: Elaboración propia.

Cuando se implementan los dos fragmentos del código se realiza una prueba donde el microcontrolador PSoC prende y apaga el led indicador que tiene cuando se colocan valores superiores a 0 en el bloque proporcional de la interfaz gráfica. Como se indicó anteriormente, los datos que se envían desde MatLab® llegan al microcontrolador por medio del bloque UART, figura 4, el cual permite la comunicación de manera continua y además acepta los valores que se requieren para su reprogramación total o parcial, además como el microcontrolador posee dos bloques UART, el segundo se utiliza para la reconfiguración del segundo microcontrolador.

# 3.3. Desarrollo del hardware de estructura básica

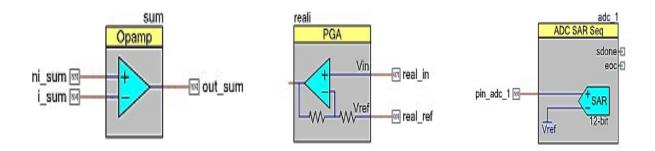

La estructura básica de un control en lazo cerrado para la aplicación de los datos obtenidos desde Simulink® y GUI de MatLab® se realiza sobre la familia PSoC de la gama 5 que posee: bloques OPAMP, que proporcionan un bloque de funcionamiento análogo a partir de un digital; los bloques PGA, para funcionamiento en modo proporcional de tal manera que puede multiplicarse una señal por una constante multiplicativa y la salida será una señal con un valor proporcional establecido; UART; y ADC, que funcionan de manera lineal por lo cual se agrega una parte digital donde se pueden sumar o multiplicar señales, pero no de manera análoga si no de manera digital; compatibles completamente con la actualización del entorno de programación PSoC creator 3.3. Ver figura 5.

Figura 5: Módulos: Opamp, entradas se configuran análogas por el propio entorno de desarrollo; PGA, Vref debe ir a tierra y vin será cualquier señal; ADC SAR, conversor Análogo Digital.

Fuente: Elaboración propia.

#### 4. Aplicación en la planta

Para la planta de nivel se realiza una prueba en funcionamiento, encontrándose características que

permiten establecer los siguientes parámetros de funcionamiento.

#### 4.1. Válvula de control proporcional

Funciona de 0 a 40 mA, con lógica inversa; esto quiere decir a que a mayor corriente menor apertura de la misma; esta válvula cuenta con la característica que a 90Kpa se cierra completamente a una corriente de 20 mA, por lo cual el rango de trabajo será de 0 a 20 mA, teniendo en cuenta los acoples de necesarios para su funcionamiento, figura 6.

#### 4.2. Sensor de nivel ultrasónico

Se encuentra en el segundo tanque de la planta; entrega los siguientes valores mínimos y máximos: cuando el tanque está lleno 19,3 mA, y si está vacío 3,9 m; lo cual es ideal para la realimentación de un lazo de control.

# 4.3. Sensor de nivel de presión diferencial

Entrega valores en corriente, pero no es ideal puesto que su valor mínimo es de 6,4 mA y su valor máximo es de 14,2 mA. Lo anterior sucede porque para un tanque de mayor proporción sería necesario realizar un circuito que trasforme el valor mínimo en 4 mA y el valor máximo en 20 mA. Por razones de facilidad en el circuito se opta por descartar el uso de este sensor, figura 6.

Figura 6: Válvula de control proporcional, y Sensor de presión diferencial.

Fuente: Elaboración propia.

# 4.4. Válvulas de apertura de líquido

Como la planta funciona como un lazo cerrado el cual permite que el líquido recircule continuamente desde el tanque de almacenamiento, este pasa por la tubería y la válvula proporcional hasta llegar al tanque donde se encuentran los sensores de nivel, y ciertas válvulas manuales y digitales permiten que el líquido vuelva al

tanque inicial. Estas válvulas funcionan con 24v de tal manera que presentan total apertura o total cierre, por lo cual no se puede variar la salida proporcional del líquido; de esta manera se opta por usar una válvula de apertura manual que se graduará de manera que en estado de nivel estable el flujo de entrada sea igual al de salida.

#### 4.5. Tanques de la planta

Los tanques de almacenamiento de líquido son dos y uno de ellos se subdivide en otros dos por lo cual se puede decir que se tienen 3 tanques donde dos de ellos cuentan con sensores de nivel; y por efecto de gravedad las válvulas de apertura permiten la recirculación del líquido al tanque de almacenamiento, debido a esto el líquido se pone en circulación gracias a una bomba de nivel de líquido que funciona a 24v.

#### 4.6. Prueba con la planta sin controladores

Se establece como lineamiento para observar el funcionamiento de la planta de nivel. Se realizan pruebas en lazo abierto con el objetivo de establecer el comportamiento que tiene la planta sin controladores que modifiquen el funcionamiento

#### 5. Resultados

Los resultados obtenidos con el sistema encuentran parámetros, no solo de manera análoga sino también de manera digital, en los módulos de procesamiento interno del PSoC que permiten ampliar la gama inicial de operaciones.

#### 5.1. Interfaz gráfica

La interfaz gráfica final permite simular o reprogramar los dos microcontroladores con alguno de los valores que el usuario necesite; de esta manera se cuenta con dos simulaciones y con posibilidades de reprogramación de hardware. En el caso del panel, donde el sistema simula la aplicación de la estructura básica de control -que en este caso es la planta de nivel de líquido *AMATROL* T5552- se simula a partir de una

función de transferencia, (Ogata, 2017), que tiene unos parámetros físicos parecidos al de la planta. Debido a que se pueden producir errores humanos en la aplicación, se estableció que, si el usuario utiliza la opción planta, el controlador 1 deshabilita su funcionamiento y se dedica exclusivamente al lazo de control, evitando así que el usuario tenga alguna señal conectada al microcontrolador pudiendo generar daños al sistema.

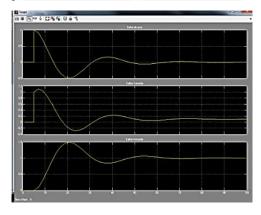

Figura 7: De arriba a abajo. Selección de los parámetros del controlador, Simulación de los parámetros y resultado en el osciloscopio de MatLab®.

Pero, si el usuario desea tener el lazo de control habilitado y además la posibilidad de utilizar el segundo microcontrolador, podrá hacerlo; de esta manera se tendrán varias opciones en el sistema que se pueden verificar en el hardware, como lo muestra la figura 7.

### 5.2. Algoritmo de reprogramación

Debido a que el algoritmo de reprogramación debía estar en dos partes -puesto que se reconfigura el hardware a partir de los valores que el software -a través de la interfaz gráfica- acepte, el estudio previo de las posibilidades de comunicación que posee PSoC compatibles con MATLAB permitió que se obtuviera un resultado satisfactorio tanto en las pruebas básicas de comunicación como en las pruebas finales.

Como el bloque UART establece una comunicación continua y sin percances, la reconfiguración de los bloques de PSoC es posible en cualquier momento de

la simulación o montaje. En consecuencia, permite que el usuario tenga tanto la opción de utilizar los bloques de dos lazos de control, como la posibilidad de utilizar un lazo de control diseñado para la planta de nivel de líquido y un lazo de control extra para utilizarlo en algún evento que crea conveniente, además de las posibilidades digitales de suma y multiplicación que cada uno de los bloques le permite.

# 5.3. Aplicación de la estructura básica en los microcontroladores

Debido a que las opciones que se pueden obtener de PSoC se realiza por medio de sus diferentes arreglos internos, el utilizar la capacidad conmutada para la reconfiguración de parámetros en el microcontrolador hizo posible obtener varios resultados sin la necesidad de variar parámetros externos o físicos en el mismo; por tanto, por medio de comandos de software se variaron parámetros que generaron resultados satisfactorios.

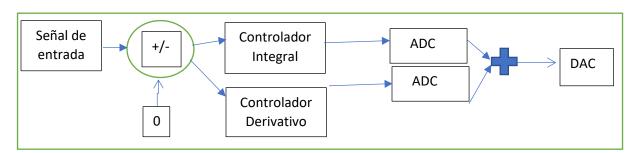

El procedimiento propuesto para la obtención de resultados de cada uno de los bloques inicia con un control en lazo cerrado en el que pueda variarse, por separado, los parámetros del bloque proporcional, el bloque integral o el bloque derivativo, dejando los bloques de suma y resta como se muestra en la figura 8.

Figura 8: Estructura utilizada para obtener resultados individuales de cada controlador.

# 5.4. Resultados del bloque proporcional PGA

El bloque PGA de PSoC permite hacer una analogía similar a la de un bloque proporcional que funciona a partir de amplificadores operacionales puros; como la lógica de PSoC se basa en capacidades conmutadas no se tienen las mismas posibilidades de ganancia, es decir: las ganancias lineales que se pueden obtener a partir de la variación física de resistencias no se pueden obtener utilizando el bloque PGA puesto que la variación física de componentes permite un rango de -muchas veces lineal otras veces posibilidades resultados logarítmica. Los obtenidos son satisfactorios.

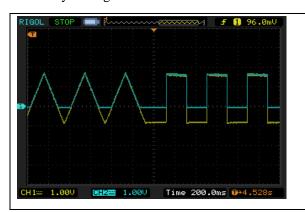

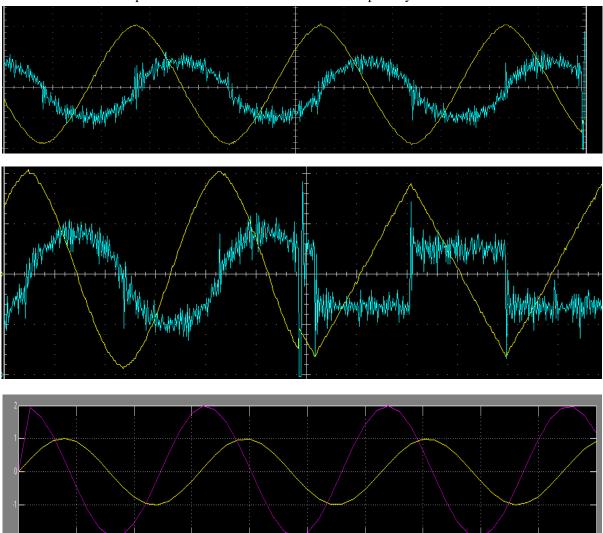

Puesto que el bloque PGA solo funciona con valores mayores a cero, la parte inferior de la señal de entrada se pierde puesto que no cumple con este requerimiento, como se muestra en la figura 9, derecha y abajo. Por medio de la gráfica se puede observar que el valor que entra al microcontrolador es el mismo de salida - ya que la escala y la magnitud son las mismas en el hemiciclo

positivo-. El bloque PGA permite la configuración de varios valores en su sección de ganancias permitiendo obtener varios resultados, debido a que esta variación no es lineal las ganancias pueden llegar a saturar la salida cuando se salta de una a otra. Con el fin de obtener señales que no contengan ningún tipo de ruido se puso un condensador de 104 en paralelo a la salida la línea de referencia obteniéndose el resultado comparativo de las figuras 9 - superior- -y en medio-. Esta última muestra una señal contaminada con ruido a causa de los parámetros de capacidad de PSoC. y la figura 9 -inferior- donde este efecto se reduce a causa del condensador de salida.

A pesar de que las ganancias del PGA no se pueden variar de manera lineal como se varía un potenciómetro en un amplificador inversor, son útiles y permiten una variedad de opciones de trabajo en laboratorio pues el PGA de adecuarse a las señales de entrada, de esta manera se obtienen resultados como el de la figura 9, superior.

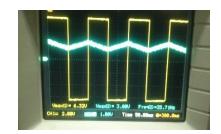

*Figura 9:* Superior izq.: Ganancia 1 del bloque PGA, con una señal triangular y una cuadrada; superior derecha: con una señal seno y triangular; Ganancia 1 del bloque PGA; segunda: Señal en amarillo: señal de entrada, Señal en azul señal de salida. PGA ganancia 2; tercera: Señal en amarillo: señal de entrada, Señal en azul señal de salida. PGA ganancia 2 más condensador conectado entre la salida y la referencia; inferior: Señal en amarillo: señal de entrada, Señal en azul señal de salida. PGA ganancia 7 más condensador conectado entre la salida y la referencia.

### 5.5. Resultados del bloque integral.

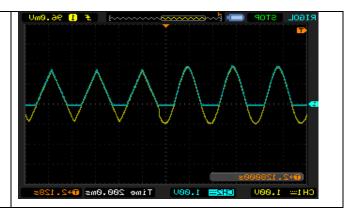

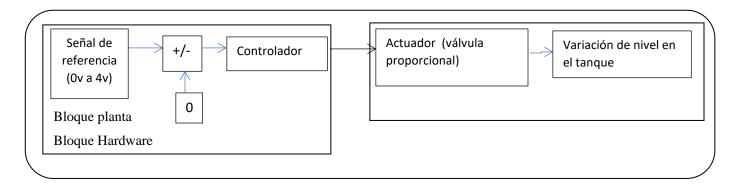

6. El bloque Opamp que se utilizó en PSoC, a pesar de ser de lógica conmutativa capacitiva, permitió la posibilidad resultados integrales a partir de la variación por código de los parámetros internos y externos, dando como resultado la figura 10.

Figura 10: superior: Señal en amarillo: señal de entrada, Señal en azul señal de salida; En medio: señal en amarillo: señal de entrada, Señal en azul señal de salida. Integral de una señal cuadrada; inferior: señal en amarillo: señal de entrada, señal en morado: señal de salida. Integral de una señal cuadrada, según Simulink®.

En las figuras anteriores, los resultados prácticos en la implementación del controlador integral son satisfactorios debido a que se asemejan a resultados prácticos obtenidos en Simulink, como lo muestra la figura 10 inferior.

# 6.1. Resultados del bloque derivativo.

El bloque Opamp, que se utilizó en PSoC a pesar de ser de lógica conmutativa capacitiva, dio la posibilidad de resultados derivativos a partir de la variación por código de los parámetros internos y externos dando como resultado obtenido en la figura 11, superior y media.

Figura 11: Superior: señal en amarillo: señal de entrada, Señal en azul señal de salida. Derivada de una señal seno; media: Señal en amarillo: señal de entrada, Señal en azul señal de salida. Derivada de una señal seno y triangular; inferior: Señal en amarillo: señal de entrada, Señal en morado: señal de salida. Derivada de una señal seno, según Simulink®.

Fuente: Elaboración propia.

Como se muestra, los resultados prácticos en la implementación del controlador Derivativo son satisfactorios debido a que se asemejan a resultados prácticos obtenidos en Simulink, como lo muestra la figura 11, inferior.

#### 6.2. Aplicación en la planta de nivel.

Igual que el desarrollo del software y el hardware, la aplicación en la planta de nivel de líquidos se hace por etapas. En la primera prueba se retoman los resultados obtenidos de experimentación en la planta. De acuerdo en esto, el modo de actuar de la planta muestra que si se desea controlar el actuador se deberá modificar la lógica inversa con la que funciona la válvula.

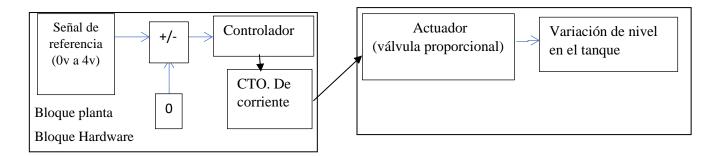

#### 6.2.1. Prueba en lazo abierto.

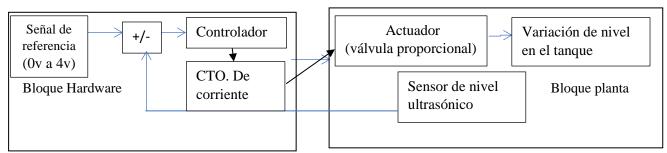

De los antecedentes de la planta, habrá dos bloques para realizar la aplicación: uno el bloque hardware y el otro bloque planta. El bloque hardware tendrá la función de generar la señal de referencia, modificar el controlador y acondicionar la señal de realimentación. Por otro lado, el bloque planta estará compuesto por el actuador (válvula proporcional), y los tanques de líquido donde se verificar la variación del nivel.

Figura 12: Diagrama de bloques para la aplicación del hardware reconfigurable en la planta.

Fuente: Elaboración propia.

Como se observa en la figura 12, la prueba en lazo abierto del hardware junto con la planta permite observar el acoplamiento del controlador junto con los sistemas propios de la planta; de esta prueba se corrobora: la lógica inversa de la válvula proporcional-la cual funciona de 4 a 20Ma- obliga a realizar un circuito que permita un comportamiento lineal del controlador sobre la planta. Por lo cual se hace una segunda prueba, figura 13.

Figura 13: Diagrama para realizar pruebas conjuntas entre el hardware y la planta con un circuito que modifique la lógica inversa de la planta.

# 6.2.2. Prueba en lazo abierto con circuito de corriente.

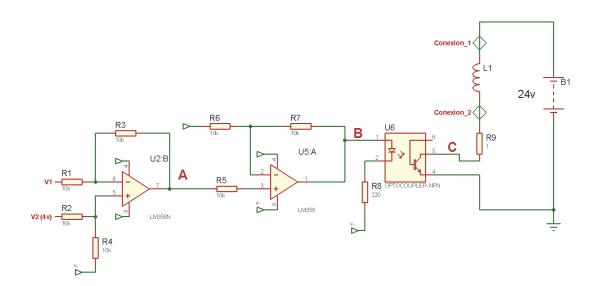

La prueba en lazo abierto de la planta junto con un circuito que acondiciona la señal de control y permite la aplicación del hardware de manera lineal sobre la planta, se documenta en los resultados de la tabla 2, al igual que la implementación del circuito de corriente diseñado, figura 14.

Como se muestra en la tabla 2, el voltaje v1 es el voltaje que proviene del controlador, el voltaje v2 es un voltaje fijo de 4 voltios que sirve de referencia, después esta diferencia de voltajes en el punto de medición A, es multiplicado por una constante de amplificación de 3, de tal forma que al llegar al opto acoplador, la corriente que se encuentra en el punto de medición C controlará la apertura de la válvula. De tal forma que con las señales de referencia controlan directamente la apertura y cierre de la válvula proporcional.

Figura 14: Circuito para modificar la lógica de apertura de la válvula.

Tabla 2

Puntos de medida en los 3 experimentos realizados.

| V2(voltios) | V1(voltios) | A (V2-V1) | B (A*3) | C (mA) | Apertura de la |

|-------------|-------------|-----------|---------|--------|----------------|

|             |             |           |         |        | válvula        |

|             |             |           |         |        | proporcional   |

|             |             |           |         |        | (%)            |

|             |             |           |         |        |                |

| 4           | 0           | 4         | 12      | 20     | 0              |

| 4           | 2           | 2         | 6       | 11     | 50 – 60        |

| 4           | 4           | 0         | 0       | 4      | 100            |

Fuente: Elaboración propia

#### 6.2.3. Prueba en lazo cerrado

Cuando las pruebas respectivas sobre el funcionamiento de la planta en lazo abierto y cerrado muestran que el controlador puede modificar la variación de nivel en el tanque, por medio de la apertura y cierre de la válvula proporcional, se realiza una última

prueba donde se completa el lazo de realimentación con un sensor ultrasónico de nivel el cual funciona por colector abierto de tal manera que al cerrar el circuito interno por medio de algún componente externo se pueden tomar medidas en corriente o voltaje.

*Figura 15:* Diagrama para realizar pruebas conjuntas entre el hardware y la planta con sensor de nivel ultrasónico.

Fuente: Elaboración propia

Como se muestra en la figura 15, el sensor de nivel ultrasónico perteneciente al bloque planta, permite completar el lazo cerrado, permitiendo la verificación de la aplicación del controlador sobre la planta.

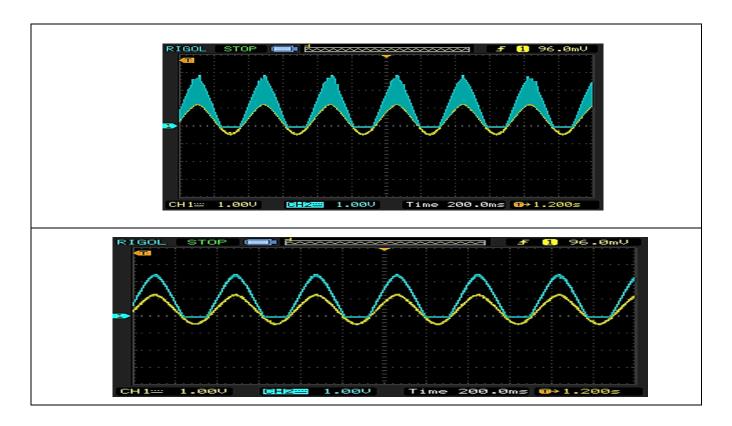

Como uno de los objetivos del sistema era la implementación del lazo de control en la planta de nivel

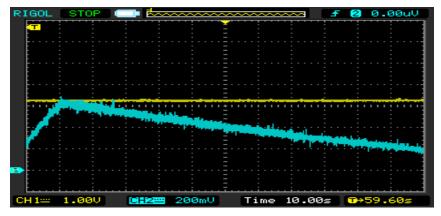

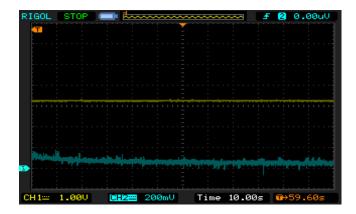

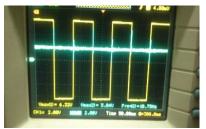

de líquidos *AMATROL T5552*; para obtener resultados y poderlos comparar se tomaron dos señales: la señal de referencia y la señal de error; esta última se obtiene de la salida en el restador. Los resultados obtenidos muestran con claridad la variación de la señal de error frente a la señal de referencia, figura 16.

Figura 16: Señal en amarillo: señal de referencia; señal en azul: señal de error.

Fuente: Elaboración propia

Para evitar la variación de la señal de referencia se dejó estática en el valor de 3,09v, lo cual permite que el nivel del tanque el cual se quiere controlar sea de 7, como lo muestra la figura 17.

*Figura 17:* Tanque nivel 3.09v, equivalente al nivel 7 de llenado y la estructura externa del tanque.

Fuente: Elaboración propia

Continuando con el seguimiento de la señal de error y la señal de referencia, la figura 18 muestra en la segunda parte del seguimiento gráfico que se le hizo a la señal donde se concluye que la señal con la aplicación del lazo de control se muestra que la señal de error llega a 0.

*Figura 18:* señal en amarillo: señal de referencia, Señal en azul: señal de error. Debido a la aplicación del controlador PID, cada uno con ganancia 1.

# 7. Consideraciones finales

# 7.1. Sumador digital.

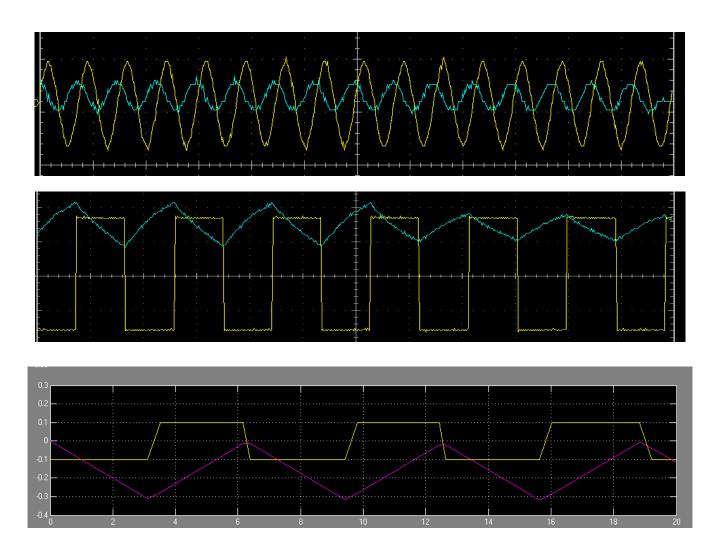

Utilizando los bloques digitales se hace una prueba con

el sumador digital, el procedimiento para obtener resultados se muestra en la figura 19

*Figura 19:* Estructura utilizada para obtener resultados individuales de cada controlador digital.

Fuente: Elaboración propia

Para este fin se integra y deriva la misma señal de la figura 20; esta señal se configura con parámetros de

frecuencia y amplitud que permiten visualizar tanto la integral como la derivada.

*Figura 29:* De IZQ. a DER. Señal cuadrada original, Señal cuadrada y su integral, Señal cuadrada y su derivada.

Cuando se configura la señal de entrada y se obtiene del integrador y del derivador una señal que permita visualizar las características individuales de cada operación se procede a configurar en la interfaz gráfica

el accionamiento de los módulos ADC y del módulo DAC para permitir la lectura, operación y publicación de los resultados, figura 21.

*Figura 21:* De Izq. a Der. En azul la derivada de una señal cuadrada, amarillo integral de una señal cuadrada, en Azul la suma de la derivada y la integral.

Fuente: Elaboración propia.

#### 8. Conclusiones

• Los parámetros de los bloques integral y derivativo son negativos, lo que quiere decir que cualquier señal positiva que sea operada por el amplificador saldrá con magnitud inversa. Esto se solucionó reemplazando los valores de referencia los cuales usualmente son cero; en el

caso de los módulos OPAMP de PSoC ese terminal se alimentó

con un valor offset el cual permitió visualizar la parte negativa y positiva de la operación.

• El control de los valores en el potenciómetro digital se realiza por medio de

varios pines que permiten la variación hacia arriba o hacia abajo del valor. En cierta prueba se encontró que los valores integrales y derivativos presentaban potenciales dañinos para el microcontrolador -cuando el valor del potenciómetro estaba por debajo de los 50K- por tal motivo se colocó una resistencia fija de 50K al potenciómetro digital. Dando como resultado

que los valores de resistencia variaran entre 50k y 150K

#### Reconocimientos

A los Grupos de Investigación INTEGRA y SciBas de la Universidad Distrital Francisco José de Caldas Facultad Tecnológica por su apoyo y asesoría en la implementación de la arquitectura y del prototipo.

# Referencias

- Angulo, A., Martínez, F., y López, G.(2017). Almacenamiento de energía usando ultracondensadores en sistemas fotovoltaicos autónomos. *Vis. Electron.*, vol. 11, no. 1, pp. 30-39. https://doi.org/10.14483/22484728.128

- Bas-Gago, I. (2010). Emulador de un microcontrolador PIC 16F84 basado en una FPGA. Cataluña: http://hdl.handle.net/10609/1004,Univ ersitat Oberta de Catalunya.

- Borges, C. (2011). páginas personales. Obtenido de algoritmos Bioinspirados: paginaspersonales.deusto.es/cruz.borge s/Papers/10APIAXXI.pdf

- Briñez de León, J., Fandiño-Toro,H., Restrepo-Martínez,A., Branch-Bedoya, J. (2016). Análisis de resolución en imágenes de fotoelasticidad: caso carga dinámica. *Vis. Electron.*, vol. 11, no. 1, pp. 69-75,.

https://doi.org/10.14483/22484728.127

- Cabaiguan, Joven club de computación (s.f.). EcuRed. *Computadora analógica*. www.ecured.cu/Computadora\_anal%C 3%B3gica

- Cabrera-López. J. (2007). implementación de filtros análogos usando PSoC/FPAAs. Cali, Colombia.

- Cabrera-López, J., y Velasco-Medina, J. (2011).

Diseño e Implementación de un

Sistema Embebido para el

Procesamiento de Señales

Ultrasónicas. Revista Colombiana de

física, (Vol. 43), No.1,

- Cadena Beltrán, A. F. . (2020). Realidad aumentada en el desarrollo del postconflicto colombiano : Augmented reality in the development of the

- Colombian post-conflict. Noria Investigación Educativa, 1(5),54–76. https://doi.org/10.14483/25905791.1645

- Caicedo, C., y Smida, A. (2016). Intensidad informacional para la longitudinalidad asistencial en sistemas de salud. Vis. Electron., vol. 10, no. 1, pp. 83-95. https://doi.org/10.14483/22484728.1161 2

- Costa, N., Pujana, F., Colombo, R., Alcoleas, Colombo, R. (2010). Red de Sensores para Monitoreo Costero de Temperatura utilizando Dispositivos Analógicos digitales Reconfigurables. Congreso de microelectrónica aplicada, (págs. 239-241).

- Custodio A. (1999). Sensores inteligentes: la revolución tecnológica de la instrumentación.

http://www.raco.cat/index.php/Buran/ar ticle/viewFile/178815/240291

- Delgadillo, A., Piraján , R. (s.f.). Uso de arreglos analógicos programables (FPAA) en instrumentación industrial: http://revistas.udistrital.edu.co/ojs/index.php/Tecnura/article/view/6278

- Dominguez, I., Rodriguez, F., Montero, M.(2010). Sistema de digitalización de señal basado en FPGA y configurado utilzando Matlab. Cientifica.

- Duarte Barón, K., y Borrás Pinilla, C. (2016). Generalidades de robots paralelos. Vis. Electron., vol. 10, no. 1, pp. 102-112. https://doi.org/10.14483/22484728.1171

- Enríquez, W, Nazate P., y Marcillo, O. (2018).

Prototipo DAS basado en FPGA de 12 canales para monitoreo geodinámico.

Vis. Electron., vol. 12, n.º 1, pp. 73-82.

- Espinar, M. (2011). Diseño e implementación de un emulador fotovoltaico para el testeo de inversores en un entorno de programación Simulink y desarrollo de una interfaz HMI.

- Espinosa, A. (2012). Optimización de distribución de carga en encaje de prótesis para amputado a nivel transfemoral. Santiago de Cali.

- Fuertes, V. (2011). Control adaptativo Bioinspirado utilizando circuitos de señal mixta PSoC.

- García, D., Casas, B. y Regalia, M. (2016).

Origen de la vida basada en la complejidad biológica de los organismos: una revisión. Vis.

Electron., vol. 10, no. 1, pp. 113-124. https://doi.org/10.14483/22484728.1164

- Gómez-Almadana, (2007). A. Diseño y realización de un simulador de radar. Publicacionesfac.https://www.google.com.co/url?sa=t&rct=j&q=&esrc=s&source=

web&cd=2&cad=rja&uact=8&ved=0ahUK Ewjti4yobTMAhWKth4KHSPNBVAQFggdM AE&url=http%3A%2F%2Fwww.publicacio nesfac.com%2Findex.php%2FTecnoESUFA %2Farticle%2Fdownload%2F198%2F322& usg=AFQjCNESYS4v3BPISZXfl-f7

- Guerrero, D. (2008)). Manual de Interfaz Gráfica de Usuario en Matlab, 2008. www.dspace.espol.edu.ec/bitstream/123 456789/10740/19/%255Bmatlab%255D\_ MATLAB\_GUIDE.pdf

- Gutierrez R, Lambas J, Albarracin, P., y Vazquez T. (2006). Solid Edge v16. Guia deReferencia. Madrid, España.

- Herrera-Cubides, J., Gaona-García, P.,

Montenegro-Marín, C., SánchezAlonso,S, y Martin-Moncunill, D.

Abstraction of linked data's world.

Vis. Electron., vol. 13, no. 1, pp. 5774, feb. 2019.

https://doi.org/10.14483/22484728.143

97

- Jiménez, L. Parrado, J., Quiza, C., Suarez, C.(s.f.). Modulación multiprotadora OFMD. Academia y desarrollo, 30-34 pp.

- Jiménez Núñez, S., y Panchi-Campos,

D.(2011). Diseño e implementación de

un modulador y un demodulador

NQAM empleando XILINX ISE,

System generator y Simulink sobre una

tarjeta de entrenamiento basada en un

FPGA de XILINX.

- J. James, (2019, enero). Strength benefit of sawdust/ wood ash amendment in cement stabilization of an expansive soil. Revista Facultad de Ingeniería, vol. 28 (50), pp. 44-61. https://doi.org/10.19053/01211129.v28.n50.2019.8790.

- Icaza, M., y Estrada J., Simulación e

Implementación en FPGA de un

Esquema de Codificación del Canal

sujeto al Estándar de Wimax.

biblioteca.universia.net/html\_bura/fich

a/params/title/simulacionimplementacion-fpga-esquemacodificacion-canal-sujeto-estandarwimax/id/52152418.html

- Martínez, M. (2012). Universidad de Valencia.

Obtenido de Diseño De Filtros FIR:

ocw.uv.es/ingenieria-yarquitectura/filtrosdigitales/tema\_3.\_diseno\_de\_filtros\_fir

.pdf

- Montoya, W. Congreso Argentino de Sistemas Embebidos. Anemómetro A ónemmetro Ultrasónico Ul o itrasnco 3D empleando Arquitecturas A i. www.sase.com.ar/2011/files/2011/02/57

Anemometro\_Ultrasonico\_3D\_empleand o\_Arquitecturas\_Analogica-Digital\_Reconfigurables.pdf

Montiel, O., Ayala, M., y Ripoll, L. (2016). Diseño y simulación de antena no resonante: guía de onda de ranuras

- para 30 GHz. Vis. Electron., vol. 10, no. 1, pp. 49-56. https://doi.org/10.14483/22484728.1161

- Morales, I., Orozco C., y Gamarra, M. (2014).

Enlace Inalámbrico Usando Módulos

XBee para la Visualización de una

Señal Analógica a Través de

LabVIEW y Dispositivos moviles.

Twelfth LACCEI Latin American and

Caribbean Conference for Engineering

and Technology (LACCEI'2014).

Guayaquil, Ecuador.

- Moroz, M., Jasinski, R., Pedroni, V. (2012). Requisitos para adoção de sistemas operacionais embarcados. Vis. Electron., vol. 6, n.º 1, pp. 89-97.

- Mota, S. (2008). Bio-inspired circuits for realtime motion evaluation.

- Ogata, K. (2017). Ingeniería de control moderna. 5a. Edición, Pearson Education, S.A., Madrid.

- Palacios, E., Remiro, F., y López,L.(2006). Microcontrolador PIC16F84 Desarrollo de proyectos. Madrid, Alfaomega.

- Pérez, M., Cavanzo, G, y Villavisán-Buitrago, F. (2018). Sistema embebido de detección de movimiento mediante visión artificial. *Vis. Electron.*, vol. 12, n.º 1, pp. 97-101

- Saavedra E. J. (2008). Técnicas para la disminución del tiempo de ejecución en algoritmos de procesamiento en el dominio de la frecuencia. Vis. Electron., vol. 1, n.º 1, pp. 62-70.

- Salamanca, T. (2018). Prototipo para monitorización de signos vitales en espacios confinados. Vis. Electron., vol. 12, no. 1, pp. 83-88. https://doi.org/10.14483/22484728.1340

- Romero, O., Barón Velandia, J., y. Espitia-Cuchango, H. (2015). Prototipo de un controlador de tráfico para una intersección semaforizada. Vis. Electron., vol. 9, n.º 1, pp. 58-66.

- Torres, I., Padrón, Y., Hernández, A. Taboada. (2012) Implementación de filtro FIR en sistemas programables en un chip. rielac.cujae.edu.cu/index.php/rieac/arti cle/view/61/pdf\_55

- Urbina W., y Martínez F. (2012). Implementación de un electromiógrafo con interfaz USB. TECNURA, 117– 130.

- Vergara, J., y Estrada R. (2008). Simulación de un Esquema de Modulación / Demodulación OFDM Utilizando un Modelo de Canal Multitrayectoria". Guayaquil – Ecuador.

Vergara J. y Estrada, R. (2008). Simulación de un Esquema de Modulación / Demodulación OFDM Utilizando un Modelo de Canal Multitrayectoria. Guayaquil – Ecuador.