# DISEÑO DE UN SISTEMA DE COMUNICACIÓN INALÁMBRICA PARA PAGO ELECTRÓNICO DE PEAJES

Giovanni Bermúdez\* giovanni@cmua.uniandes.edu.co

This document presents academics experiences about the design of a wireless communications system at microwave frequencies for applications in electronic toll collection. This work was based in Gallium Arsenium (HgaAsIV – F20) technology of Gec-Marconi Company.

#### Introducción

l crecimiento del flujo vehicular en Colombia, especialmente de automotores de carga y de pasajeros en las vías, conlleva un mayor control y mantenimiento de las vías. Por esta razón el gobierno nacional ha incrementado las concesiones de carreteras a empresas privadas para su construcción y mantenimiento, incrementando a su vez el número de peajes por tramo, para su autofinanciación.

Pensando en dar una solución a los inconvenientes así descritos, en este artículo se plantea una alternativa tomada de avances en pagos automáticos de Europa, en donde se plantea un sistema de comunicaciones conformado por una estación base a 5.8 GHz y una estación móvil a la misma frecuencia. El sistema de codificación y decodificación de la información se realiza mediante codificación Manchester. En este artículo se explican los tipos de enlaces utilizados, los dos sistemas (estación base y móvil) y su forma individual de operación; complementariamente se muestran los resultados de las implementaciones realizadas y el estado actual del proyecto. La Herramienta CAD utilizada en el diseño del sistema de comunicaciones es HP-EEsof Series IV, versión 6.0.

### Descripción del Sistema de Comunicaciones

Las regulaciones Europeas y el FCC (Federal Communication Commission) han establecido bandas tipo ISM dentro de un rango de frecuencias definido para sistemas inalámbricos para pago electrónico de peajes. Esta banda está definida en un rango de frecuencias de 5.725 a 5.850 GHz; el sistema estándar europeo establece el rango de frecuencia de 5.795 a

<sup>\*</sup> Ingeniero Electricista Universidad Nacional de Colombia, Magister en Ingeniería Electrónica y de Computadores, Universidad de los Andes. Profesor adscrito a la Facultad Tecnológica de la Universidad Distrital Francisco José de Caldas, Ingeniero Investigador del Centro de Microelectrónica de la Universidad de Los Andes en el área de Arsenuro de Galio (GaAs) y diseño de MMIC's.

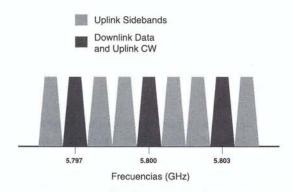

5.805 GHz para estos tipos de enlaces, con subbandas adicionales de 5.805 a 5.815 GHz y seis canales con frecuencias centrales de 5.797, 5.800, 5.803, 5.806, 5.809, 5.812 GHz.

La diferencia entre canales de 3 MHz está concebida para asegurar que el producto de la intermodulación no caiga dentro de la banda de recepción de la estación base. En la Figura 1 se presenta un gráfico en el cual pueden observarse los dos tipos de enlaces y las frecuencias dentro del rango especificado [6]. Adicionalmente, una separación de 1 MHz alrededor de la frecuencia central de cada canal es reservada para realizar el enlace entre módulos de comunicaciones del sistema.

Figura 1. Tipos de Enlaces y Bandas de Operación

El sistema de comunicación está conformado por dos módulos que operan a una frecuencia central de 5.8 GHz con un ancho de banda de 1 MHz. Cada módulo posee como principio de funcionamiento un sistema Half-Duplex [2] que reduce su complejidad y costo. El módulo de transmisión es sincrónico, y se constituye en un medio eficiente de transmitir información a alta velocidad; también es compatible con el computador central de control del sistema de comunicación basado en el protocolo HDLC.

El primer sistema es llamado Estación Base Terrestre (EBT). Este sistema siempre está emitiendo una señal continua modulada tipo ASK, seleccionada como método de modulación por presentar características sencillas para su detección. Por esta razón, se especifica que este módulo es siempre activo. La Estación Móvil (EM) utiliza un diodo para demodular la señal ASK y sincronizarse adecuadamente para realizar la comunicación. La información del

reloj requerido para la sincronización del protocolo es transmitida en la señal de dato usando un decodificador de Código Manchester.

La Estación Móvil posee un funcionamiento pasivo, es decir, inicia los enlaces de comunicaciones con la EBT una vez entre en la zona de pago predeterminada. Con el diseño de este enlace microondas se pretende que el dispositivo a bordo de la EM (ubicada en el vehículo), sea de bajo perfil y no muy costoso. Por lo anterior, se ha considerado un diseño sin oscilador local para esta unidad de comunicación, reduciendo tamaño y costo.

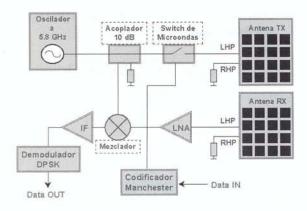

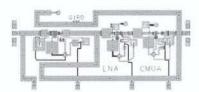

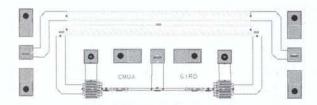

El módulo de recepción de la EBT consta de un oscilador local a 5.8 GHz, cuya señal portadora esta acoplada a un mezclador de rechazo de imagen, quien a su vez recibe la señal de RF modulada a 5.799 GHz mezclando con el LO (Local Oscillator). La señal de salida del mezclador posee un ancho de banda de 1 MHz y es amplificada utilizando un amplificador IF. De igual forma contiene un demodulador DPSK que realiza la demodulación por desplazamiento de fase extrayendo la información requerida. La etapa de transmisión consta de un modulador digital a través de un decodificador de Código Manchester, tipo pasabanda; acoplado a este dispositivo hay un conmutador de microondas (RF Switch), el cual combina la señal de la portadora con la digital para ser transmitida a través de una antena de parches con polarización circular. En la Figura 2 se presenta la ETB con todos sus módulos.

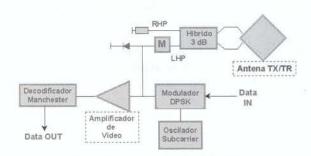

La EM está constituida por una antena que recibe la señal de excitación enviada por la EBT. Durante este proceso (denominado enlace ascendente – UPLINK), la antena recibe la portadora sin modular y esta señal es modulada por un modulador DPSK, el cual la desplaza 1 MHz de la frecuencia central. Posteriormente la modulación es retransmitida por la antena al EBT mediante un enlace descendente (DOWNLINK). En la Figura 3 se muestra un diagrama de módulos del EM. Las especificaciones del sistema de la EBT se presentan en la Tabla 1.

La finalidad de este sistema es permitir a la EBT realizar el intercambio de información con el vehículo que se desplaza a velocidades hasta de 160 Km/h, sin detenerse ni disminuir la velocidad. Esto significa que a la velocidad de transmisión de datos de 250 Kbps se requiere de una zona de

Figura 2. Módulos que conforman la EBT

Figura 3. Diagrama de Bloques del EM

| Oscilador              |               |

|------------------------|---------------|

| Frecuencia             | 5.8 GHz       |

| Potencia de Salida     | + 20 dBm      |

| Amplificador de Bajo   | Ruido (LNA)   |

| Banda de Operación     | 5.7 a 5.9 GHz |

| Ganancia               | 30 dB         |

| Figura de Ruido        | 2 dB          |

| Mezclador de Rechaz    | o de Imagen   |

| Pérdidas de Conversión | 8 dB          |

| Amplificado            | rIF           |

| Ancho de Banda IF      | 250 kHz       |

| Ganancia               | 100 dB        |

Tabla 1. Especificaciones de cada uno de los Módulos que conforman la Estación Base.

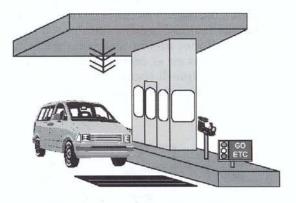

comunicación de por lo menos 10 m., con un montaje de 4 a 6 m. de altura, como se observa en la Figura 4. La polarización de las antenas permite la utilización de varios dispositivos en carriles laterales sin interferencia, ya que la respuesta será de polarización inversa.

Estas reflexiones se atenúan por la discriminización de polarizaciones cruzadas ocasionadas por las antenas, y también minimizan los efectos de reflexiones multipatrón ocasionados desde los vehículos.

Figura 4. Diagrama del Sistema de Pago Electrónico de Peajes

Figura 5. Sistema Actual de Pagos de Peajes

El sistema actual de pago de peajes (Figura 4) posee varias características principales: (i) Requiere una zona amplia para realizar el pago por parte del usuario; (ii) El automotor debe detenerse en la zona de pago; (iii) El intercambio del dinero por parte del usuario al operario crea inseguridad y alto riesgo.

El sistema que se plantea en este trabajo (Figura 5 posee mejores características que el sistema actual,

a saber: (i) El automóvil no tiene la necesidad de detenerse para realizar el pago (velocidad máxima de hasta 160 Km/h; (ii) El sistema del manejo de información se puede realizar vía satélite a una central remota (se trata de un sistema de prepago); (iii) La estructura física del sistema sería de tamaño reducido, dado que se tienen tarjeta que no alcanzarían los 15 cm² con una antena muy pequeña.

### Diseño de Módulos del Sistema de la EBT

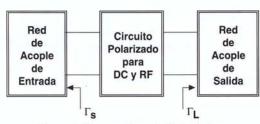

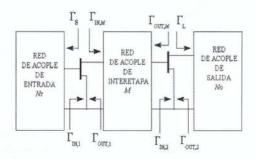

El proceso de diseño utilizado es especificado para el diseño de cualquier módulo en alta frecuencia. La técnica general de diseño utilizada fue la de parámetros de dispersión S, diseñado con una impedancia característica de 50 W. El primer paso desarrollado en la concepción de este sistema fue diseñar el oscilador local a la frecuencia de operación (5.8 GHz) [3,7]. Para este diseño se tuvieron en cuenta tres diferentes implementaciones: un DRO (Dielectric Resonator Oscillator); un RRO (Ring Resonator Oscillator) y un VCO (Voltaged Controlled Oscillator). Los acoples de microcintas realizados para cada uno de estas implementaciones fueron realizadas utilizando técnicas basadas en el concepto de resistencias negativas (principio de oscilación) con parámetros de dispersión de pequeña señal (Figura 6).

Figura 6. Esquema General del Oscilador

Las condiciones de oscilación [3,7] necesarias para el diseño del LO (Local Oscillator) son:

- El transistor debe ser potencialmente inestable a la frecuencia de operación

- Diseñar una red para obtener  $|\Gamma_{I}| > 1$

Diseñar una red de carga que satisfaga la condición anterior, es decir:

$$X_L(w_o) = -X_{IN}(w_o)$$

$$RL = \frac{|Rin(0, w)|}{3}$$

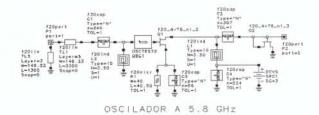

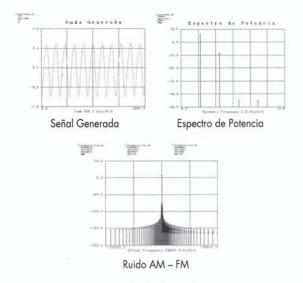

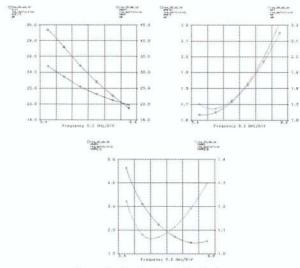

Los sistemas de sintonización para cada oscilador fueron: un resonador dieléctrico modelado a través de un circuito RLC, un anillo resonante y un diodo varactor, respectivamente. A continuación se muestra la implementación definitiva del Oscilador alcanzado mediante un VCO. Los resultados de simulaciones se presentan en la Figura 8.

Para poder ajustar mucho mejor el VCO a la frecuencia de oscilación, se utiliza un PLL (Phase Loop Locked) [4,5] como el mostrado en la Figura 9.

Figura 7. Diseño Esquemático del LO

Figura 8. Resultados de Simulaciones

Figura 9. (a) Diagrama de Bloques de un PLL; (b) PLL como Sintetizador de Frecuencia

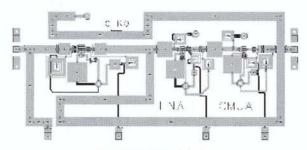

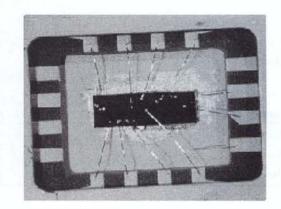

El diseño del circuito integrado para el LO se diseñó y se envío a fabricación al IMEC-Bélgica en noviembre de 1998, y actualmente se encuentra en etapa de pruebas [1]. En la Figura 10 se muestra el Layout del LO.

Figura 10. Layout del LO

Dado que no se logró obtener la potencia requerida para la salida del oscilador (Tabla 1), se diseñó un amplificador de potencia para alcanzar la potencia de salida del oscilador hacia el sistema. La característica principal de este diseño fue la no linealidad presentada en este módulo.

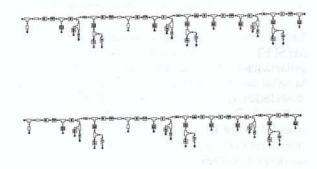

El segundo módulo diseñado fue el LNA (Low Noise Amplifier), utilizado para disminuir el ruido de la señal recibida del EM [3]. Se diseñó en tres etapas con una ganancia de potencia total de salida aproximada de 30 dB. La primera etapa tiene una ganancia de 7.6 dB con una figura de ruido de 1.0654 dB. Las dos etapas siguientes fueron diseñadas a 14 dB, cada una con el mismo transistor MESFET. La figura de ruido de la primera etapa es la más importante dado que a partir de la ecuación 1, se puede determinar la figura de ruido total del amplificador y del sistema mismo.

$$F = F_1 + \frac{F_2 - 1}{G_{A1}} + \frac{F_3 - 1}{G_{A1}G_{A2}} \dots = F_{min} + \frac{r_n}{g_s} |y_s - y_{opt}|^2$$

(1)

donde F es la figura de ruido del dispositivo;  $F_1$  es la figura de ruido de la primera etapa,  $F_2$ ,  $F_3$  son las figuras de ruido de las etapas dos y tres, respectivamente;  $G_1$  es la ganancia de potencia de la primera etapa, y  $G_2$  es la ganancia de potencia de la segunda etapa. Para el acople de las diferentes etapas se tuvieron en cuenta las siguientes condiciones:

$$\Gamma$$

S =  $\Gamma$ opt,1

$\Gamma$ IN,M =  $(\Gamma$ OUT,1)\*

$\Gamma$ OUT,M =  $\Gamma$ opt,2

$\Gamma$ L =  $(\Gamma$ OUT,2)\*

donde  $\Gamma_{\text{opt}}$  es el coeficiente de reflexión para el cual se obtienen las mejores condiciones de transferencia de potencia y figura de ruido. El criterio está basado en disminuir el VSWR tanto de entrada como de salida tal como se observa en la Figura 11.

Figura 11. Diagrama de un Amplificador de dos etapas

Figura 12. Diseño Esquemático del LNA

Figura 13. Resultados de Simulaciones

Figura 14. Layout del LNA

El diseño esquemático del LNA y los resultados de las simulaciones se presentan a continuación. El diseño del Circuito integrado para el LNA se muestra en la Figura 14.

El amplificador IF (de frecuencia intermedia) fue diseñado con condiciones normales de operación con un transistor normal (se utilizó un FET de canal n); por esto no se presenta el diseño realizado.

Para el diseño del mezclador se utilizó un transistor MESFET en configuración *Source-Común* para su polarización [4], aplicando la señal de RF al Gate y la señal de LO al *Source* con el fin de construir un mezclador resistivo. Sólo se polarizó el *Gate* al voltaje de Pinchoff con el fin de maximizar la no linealidad de la transconductancia (función de transferencia) y se diseñaron los acoples con el fin de obtener la mejor respuesta de frecuencia intermedia y rechazando por completo la frecuencia de imagen. La frecuencia de imagen es un subpro-

ducto propio de la multiplicación de los voltajes de entradas que corresponde a | 2flo-fRF|.

El diseño del mezclador es mostrado a continuación con sus respectivas simulaciones y layout del circuito integrado diseñado. En el esquemático se presentan varias cajas, estas cajas son filtros realizados para eliminar ruido presente en las señales.

Figura 15. Diseño Esquemático del Mezclador

Figura 16. Simulación de la Respuesta de la Salida del Mezclador a las Señales de Entrada: LO y RF

Figura 17. Layout del Mezclador

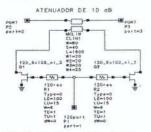

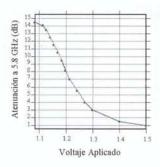

El atenuador diseñado fue realizado utilizando esquemas análogos con un mínimo de pérdidas y realizando implementación muy sencilla, como puede verse de la Figura 18. Los resultados de este diseño son mostrados en la Figura 19, y el layout del circuito integrado se presenta en la Figura 20.

Figura 18. Diseño Esquemático del Atenuador RF

Figura 19. Simulación del Atenuador

Figura 20. Layout del Atenuador RF

#### Estado Actual del Proyecto

La implementación de los dispositivos que conforman esta unidad se ha desarrollado con la ayuda del software EESOF Series IV de la compañía Hewlett Packard. Estas implementaciones han sido realizadas a nivel de esquemáticos, teniendo en cuenta la tecnología seleccionada (Gec-Marconi F20), y que serán implementados en un IC (Integrated Circuit). Cabe recalcar que todos los módulos fueron implementados con el mismo transistor MESFET y a un voltaje de alimentación de 3.3 V (voltaje estándar para estos sistemas). El módulo del amplificador de potencia es alimentado a una tensión de 6 V.

El oscilador local diseñado fue enviado a fabricación en noviembre de 1998 en el IMEC-Bélgica, y actualmente se encuentra funcionando al 90 % dado que según resultados de Test realizados al dispositivo su frecuencia de operación es de 5.856 GHz presentando un corrimiento no deseado.

Los demás módulos se encuentran en proceso de fabricación en Bélgica. Las siguientes figuras muestran fotografías tomadas al sistema fabricado.

Figura 21. Montaje realizado para pruebas

Figura 22. Montajes realizados para Pruebas

Figura 23. Circuito Integrado Fabricado

## Perspectivas del Proyecto

Dentro del proceso de diseño del sistema de comunicaciones se hace necesario optimizar la operación de la estación base e iniciar el diseño de la estación móvil. Después de diseñados los dos sistemas se realizará la implementación de cada una de las estaciones sobre un substrato de teflón, para realizar pruebas del correcto funcionamiento del sistema de comunicaciones. Estas pruebas serán llevadas a cabo en diferentes regiones del territorio colombiano, caracterizadas por su diversidad topográfica, con el fin de poder comprobar el correcto desempeño del sistema. El paso final es dar inicio a la fabricación de los circuitos integrados para su comercialización.

#### Resultados

| OSCILADOR                                    |                 |

|----------------------------------------------|-----------------|

| Tipo de Resonador                            | VCO             |

| Frecuencia de Operación                      | 5.800000549 GHz |

| Potencia de Salida                           | + 8.53 dBm      |

| Voltaje Generado                             | -0.72 a 0.6 V   |

| Tensión de Alimentación (VDS)                | 3.3 V           |

| Corriente                                    | 14 mA           |

| Area Layout                                  | 18.75 mm2       |

| Area Chip Fabricado                          | 3 mm2           |

| Tipo Encapsulado                             | 16 Pines        |

| AMPLIFICADOR DE I                            | POTENCIA        |

| Potencia de Entrada Máx.<br>(sin saturación) | 16.5 dBm        |

| Potencia de Salida Máx.<br>(sin saturación)  | +27.33 dBm      |

| Potencia de Entrada - Osc                    | 8.53 dBm        |

| Potencia Salida                              | 21 dBm          |

| Perdidas en Acople<br>(Oscilador - Amp Pot)  | 0.02 dBm        |

| Tensión de Alimentación Vos                  | 6 V             |

| Tensión de Alimentación Ves                  | -0.8 V          |

| Corriente                                    | 337 mA          |

| Area Layout                                  | 2.34 mm2        |

| Tensión de Alimentación Vos                  | 6 V             |

| AMPLIFICADOR DE         | BAJO RUIDO      |

|-------------------------|-----------------|

| Ganancia de Salida      | 29.876 dB       |

| Ganancia Máxima         | 30.97 dE        |

| Figura de Ruido         | 1.79 db         |

| VSWRIN - VSWRout        | 1.6189 - 1.0638 |

| Tensión de Alimentación | 3.3\            |

| Corriente               | 9.5 mA          |

| Area Layout             | 12.49 mm2       |

| MEZCLADOR DE B          | AJO RUIDO       |

| Potencia IF a la salida | - 95.3 dBm      |

| Potencia IM a la salida | - 95.3 dBm      |

| Frecuencia LO           | - 195 dBm       |

| Frecuencia RF           | 5.8 GHz         |

| Frecuencia IF           | 5.8 GHz + 1MHz  |

| Perdidas de Conversión  | No realizado    |

| Area Layout             | 5.83 mm2        |

| ATENUADOR DE MI         | CROONDAS        |

| Potencia de Entrada     | 20 dBm          |

| Potencia de Salida      | 10 dBm          |

| Voltaje de Control      | 1.18 V          |

| Ancho de Banda Dinámico | 2 GHz           |

| Area Layout             | 1.93 mm2        |

| AMPLIFICAD              | OR IF           |

| Ancho de Banda IF       | 250 kHz         |

| Ganancia                | 92 dBm          |

Tabla 2. Resultados obtenidos para cada uno de los módulos diseñados

# REFERENCIAS BIBLIOGRÁFICAS

- BERMÚDEZ, Giovanni. "Implementación de un Sistema de Comunicación Inalámbrico para Pago Electrónico de Peajes", Tesis de Magister. Universidad de Los Andes, Bogotá, 1999.

- BERMÚDEZ, Giovanni. "Osciladores Controlados por Voltaje (VCO's)". Universidad de los Andes, Bogotá, 1997.

- GONZALEZ, Guillermo. "Microwaves Transistor Amplifiers", Editorial Prentice Hall, 1997.

- GOYAL, Ravender. "High Frequency Analog Integrated Circuit Design". Ed. John Wiley & Sons, 1995.

- POZAR, David. "Microwave Engineering", Addison-Wesley, 1990.

- VLASITS, Támas. Koolkiewicz, E. Sambell, Alaister. "A 5.8 Ghz Microwave Link for Automatic Debiting Aplications", Microwave Journal, June 1995. pp 80-87.

- VENDELIN, G. Pavio, A. Rohde, U. "Microwave Circuit Design, Using Linear and Nonlinear Techniques", John Wiley & Sons, 1990.