# Visión Electrónica

Más que un estado sólido

https://revistas.udistrital.edu.co/index.php/visele

VISIÓN DE CASO

# Prototipo DAS basado en FPGA de 12 canales para monitoreo geodinámico

DAS prototype of 12-channel for geodinamic monitoring based on FPGA

Wilson Enríquez.<sup>1</sup>, Paola Nazate.<sup>2</sup>, Omar Marcillo.<sup>3</sup>

## INFORMACIÓN DEL ARTÍCULO

# Historia del artículo:

Enviado: 23/10/2017 Recibido: 11/11/2017 Aceptado: 12/01/2018

#### Palabras clave:

DAS FPGA Monitoreo sísmico Monitoreo volcánico Sistemas embebidos

#### Open access

# Keywords:

DAS

FPGA

Seismic monitoring

Volcanic monitoring

Embedded systems

#### RESUMEN

La directriz del presente proyecto crear un sistema de adquisición y grabación de señales sísmicas que sea compacto, confiable y flexible para adaptarse a las necesidades de trabajar en estaciones de monitoreo volcánico y sísmico. Para alcanzar el objetivo se empleó el FPGA Spartan-6 LX45 como base del sistema embebido de adquisición continua de datos a velocidad configurable hasta 50 Ksps. Además el prototipo cuenta con comunicación vía Ethernet, 12 canales de ADC de 24 bits expandible hasta 24 canales, almacenamiento de datos en memoria USB, interfaz amigable, indicador de información en LCD y sincronización de tiempo UTC mediante GPS externo. Como resultado del presente proyecto se obtuvo un dispositivo electrónico embebido para aplicaciones sísmicas como: monitoreo, refracción o reflexión y aplicaciones para estudios vulcanológicos con antenas de sensores, que además es compatible con softwares de visualización y gestión de datos sísmicos.

#### ABSTRACT

The guideline of the present project is to create a seismic digitizer. In order to be used as a seismic field station, the digitizer should be compact, reliable and flexible to adapt at field seismic station. The objective was achieved using the Spartan-6 LX45 FPGA as the basis for the embedded continuous data acquisition system with a configurable speed up to 50 Ksps. The prototype comes equipped with Ethernet communication, 12 channels with 24-bit ADC resolution expandable up to 24 channels, data storage writable to both USB and SD, a user-friendly interface, LCD information indicator and time synchronization to UTC by external GPS. As a result of the present project, an embedded electronic device was obtained that can be utilized diverse seismic applications such as monitoring, refraction or reflection and for use in sensor arrays appropriate for volcanic applications. The prototype is compatible with visualization and seismic data management software.

<sup>&</sup>lt;sup>1</sup>Ingeniero en Electrónica y Telecomunicaciones, Escuela Politécnica Nacional, Ecuador. Magister en Ingeniería de Comunicaciones, Universidad de Cantabria, España. PhD(c) Universidad Federal de Santa Catarina - Brasil. Instituto Geofísico de la Escuela Politécnica Nacional, Ecuador. Correo electrónico: wenriquez@igepn.edu.ec

<sup>&</sup>lt;sup>2</sup>Ingeniera en Electrónica y Control, Escuela Politécnica Nacional, Ecuador. Instituto Geofísico de la Escuela Politécnica Nacional, Ecuador. Correo electrónico: pnazate@igepn.edu.ec

<sup>&</sup>lt;sup>3</sup>Físico, Escuela Politécnica Nacional, Ecuador. Master of Sciences, Geology, University of New Hampshire, Estados Unidos. Doctor of Philosophy Geophysics, New Mexico Institute of Mining and Technology, Estados Unidos. Laboratorio Nacional de los Álamos, Estados Unidos. Correo electrónico personal e institucional correo electrónico: omarcillo@lanl.gov

## 1. Introducción

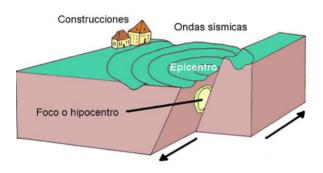

A nivel mundial existen países que son más propensos a sismos, tsunamis y erupciones volcánicas, esto se debe a que se encuentran sobre el "Cinturón de Fuego del Pacífico" [1], el mismo que concentra al 75% de los volcanes activos del mundo y en él se producen hasta el 90% de los terremotos [2]. Por esta razón es de gran interés mantener un monitoreo continuo y en tiempo real de la actividad sísmica y volcánica de las zonas en amenaza (Figura 1)

Figura 1: Propagación onda sísmica [3].

En el mercado se encuentran a disposición sistemas especializados para el almacenamiento, adquisición y transmisión de datos sísmicos, sin embargo los costos son elevados [4]. Por este motivo se consideró factible la construcción de un prototipo de bajo costo, confiable, robusto v especializado para la adquisición, almacenamiento y trasmisión de señales sísmicas que sea compatible con diferentes tipos de sensores y que incluya software de visualización y gestión de datos sísmicos. Para el diseño y construcción del prototipo se consideró diversas tecnologías de bajo costo para alcanzar el objetivo principal, que es, desarrollar un sistema determinístico que adquiera 12 señales analógicas externas de sensores sísmicos a una velocidad configurables entre 20 a 500 microsengudos cada una de forma paralela y con una alta fidelidad. A su vez el equipo guarda las señales sísmicas en un dispositivo de almacenamiento no volátil y envía vía comunicación Ethernet la información en tiempo real al centro de datos para que las señales brinden las alertas adecuadas de los eventos volcanotectónicos registrados.

Como un adicional el presente dispositivo es útil para investigación geofísica, entre los que se incluyen experimentos sismológicos de refracción para medición de ondas superficiales.

## 1.1. Sistema Embebido

Es un sistema electrónico diseñado para realizar varias funciones dedicadas en tiempo real, según sea el caso, se diseñan para cubrir necesidades específicas [5]. Los sistemas embebidos se utilizan en aplicaciones que requieran una o varias de las siguientes características [6]:

- Análisis y captura de datos a alta velocidad

- Sistemas de control a prueba de fallos para largos periodos de tiempo

- Control determinístico de procesos

Podemos encontrarlos en casi todos los sistemas que son de propósito específico como por ejemplo [7]:

- En la industria: Bombas para pozos petroleros, tiempo de operación en una refinería a prueba de fallos, telescopios con actuadores de posición nanométricos, navegador GPS, etc.

- En la aviación: aeroespacial y sistemas de defensa, piloto automático, control aterrizaje, etc.

- En comunicaciones: 5G Wireless, comunicaciones cableadas, lightwireles, routers, etc.

- En el hogar: refrigerador, sistema de aire acondicionado, robots que aspiran, cortan pasto, etc.

## 1.2. Tecnología FPGA

Un FPGA o Field Programing Gate Array es un dispositivo electrónico semiconductor con compuertas lógicas físicas reprogramables después de su fabricación, para aplicaciones específicas de extrema confiabilidad y alto desempeño [8]. Los FPGAs combinan lo mejor de las ASICs y lo mejor de los procesadores ya que no requieren un diseño personalizado y no está limitada por los núcleos disponibles, es decir, llevan a cabo distintos lazos de programación con verdadero paralelismo y cada tarea es asignada a una sección dedicada del chip de silicio obteniéndose tiempos en el orden de los nanosegundos [9]. Por lo descrito anteriormente el FPGA permite implementar algoritmos con determinismos, baja latencia, alta velocidad de procesamiento, controles en lazo cerrado y desarrollo de múltiples operaciones en un mismo ciclo de reloj.

# Ventajas [10]

- Prototipado rápido, disminuye el tiempo en llegar al mercado del desarrollo

- Costo más bajo de ingeniería comparado con las ASICs

- Capacidad para reconfiguración en campo sin necesidad de cambiar la placa principal

- Ciclo de vida largo (reduce el riesgo de obsolescencia)

- Flexibilidad

- Procesamiento en paralelo.

# 1.3. Comparación tecnología entre plataformas de programación

Antes de empezar el actual proyecto se realizó una comparación tecnológica entre diversas plataformas de programación disponibles en el mercado para elegir la que más se ajuste a los requerimientos planteados. Las plataformas como arduino, Raspberry pi, BeagleBone actualmente son muy difundidas y accesibles debido a su bajo costo, además cada una tiene fortalezas dependiendo de la aplicación que se plantee. Arduino empezó rompiendo paradigmas a inicio del siglo con el

lanzamiento de una plataforma con un microcontrolador programable al alcance de todos para desarrollo y control. Raspberry Pi y Beagle Bone black utilizan microprocesadores para ejecutar aplicaciones genéricas con una alta velocidad [11].

Por otra parte los FPGAs son dispositivos altamente confiables, determinísticos con una velocidad de procesamiento de nanosegundos los cuales se implementan en celdas lógicas reprogramables para tener un real paralelismo. Se utilizan para análisis y procesamiento dedatos que requieren altas velocidades lo que disminuye los tiempos de respuesta entre los dispositivos o sensores de entrada y el Hardware de programación.

En la tabla **1** se muestra una tabla comparativa con las principales características de las plataformas Arduino Ethernet [12], Raspberry Pi B+ [13], BeagleBone [14] y c-RIO [15,16]

Tabla 1: Comparación tecnológica de diversas plataformas disponibles en el mercado.

|                                 | Arduino Ethernet                                           | Raspberry Pi B+                                                                | BeagleBone Black                                                | cRIO-9076                                                               |

|---------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------|

| Ventaja para el<br>prototipo    | Código abierto,<br>económico                               | Es una<br>minicompuadora                                                       | Buen procesamiento e<br>interfaz externa para<br>sensores       | Baja latencia, alta<br>resolución de<br>canales ADC<br>real paralelismo |

| Controlador                     | Atmega 328                                                 | n/a                                                                            | n/a                                                             | n/a                                                                     |

| FPGA                            | n/a                                                        | n/a                                                                            | n/a                                                             | Spartan 6 LX-45                                                         |

| Procesador                      | n/a                                                        | ARM 1176JZF-S                                                                  | AM335x                                                          | n/a                                                                     |

| Voltaje de<br>operación         | 5 Vdc                                                      | 5 Vdc                                                                          | 5 Vdc                                                           | 9-30 Vdc                                                                |

| Ram                             | 2 KB                                                       | 512 Mb                                                                         | 512 Mb                                                          | 512 Mb<br>expandible                                                    |

| USB                             | si                                                         | 4                                                                              | 1                                                               | 1                                                                       |

| Ethernet                        | Si, 10/100                                                 | Si, 10/100                                                                     | Si, 10/100                                                      | Si, 10/100                                                              |

| Entradas<br>Analógicas          | 6 con 10 bits de<br>resolución                             | No incluye, pero con<br>adaptación de ADC es<br>posible                        | No incluye, pero con<br>adaptación de ADC es<br>posible         | Con módulos<br>hasta 32 canales                                         |

| Digital I/O                     | 14 con 4 PWM                                               | 40                                                                             | 69                                                              | Con módulos<br>hasta 128                                                |

| Sistema<br>Operativo            | n/a                                                        | Linux                                                                          | Linux, Android,<br>windows, cloud                               | VxWorks                                                                 |

| Entorno                         | Arduino IDE                                                | Linux, QEMU,<br>Scratchbox, Eclipse                                            | Phyton, Scratch, Linux,<br>Eclipse. Android DK                  | Labview, Xilinxs,<br>C, C++                                             |

| Multitarea                      | No                                                         | si                                                                             | Si                                                              | Si                                                                      |

| Desventaja para<br>el prototipo | Baja velocidad, uso<br>en proyectos de<br>propósito simple | Es de propósito<br>general, no es bueno<br>para manejo de<br>sensores externos | No trabaja en lazos<br>realmente paralelos y<br>determinísticos | No es de código<br>abierto                                              |

Fuente: elaboración propia

# 2. Arquitectura del sistema implementado

El prototipo desarrollado es un sistema embebido portable, de bajo consumo de energía y con una alta resolución. Además cuenta con comunicación vía Ethernet y almacenamiento de datos en memorias USB y SD removibles fácilmente por el usuario y que además cuenta con una interfaz de usuario amigable y de fácil operación.

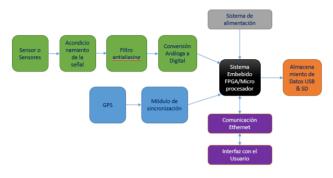

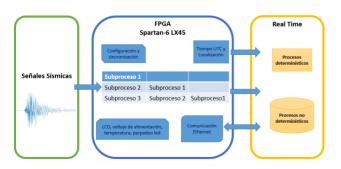

Figura 2: Diagrama de bloques del sistema.

Fuente: elaboración propia.

El sistema es preciso, confiable y cuenta con un proceso de adquisición de datos determinístico gracias a que se trabaja sobre el FPGA Spartan-6 LX45 FPGA del C-RIO 9076. En la Figura 2 se muestra un diagrama de bloques del sistema de adquisición de datos, en el que se puede observar la interacción y orden de los procesos internos y su interacción entre ellos. Para la sincronización de tiempo UTC se utiliza el módulo NI 9467 [17] con una precisión de 100 ns y los módulos NI 9239 [18] para el ingreso de las señales analógicas como entradas diferenciales con aislamiento entre canales. Los datos adquiridos se guardan en una memoria USB o SD en formato comprimido ZLib. El equipo cuenta con comunicación Ethernet mediante la cual se puede realizar configuraciones al sistema pero también sirve como medio para la trasmisión en tiempo real de los datos cuando se utiliza una red de radios digitales hasta llegar a la base de monitoreo sísmico.

# 2.1. Diseño Implementado en el FPGA

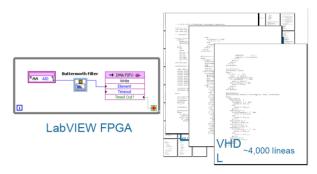

La programación en FPGA puede realizarse de 2 maneras utilizando lenguaje de bajo nivel como VHDL y Verilog o en lenguajes de alto nivel como lo son los ambientes gráficos como System Generator o Labview para FPGA. En la Figura 3 podemos observar la comparación entre el ambiente de programación VHDL y el lenguaje gráfico Labview FPGA, y podemos observar que VHDL es más extenso y de difícil implementación

para que los dos programas realicen el mismo fin; por este motivo se prefiere en el presente proyecto utilizar ambientes gráficos.

Figura 3: Comparación de código VHDL con bloques LabView para un ADC con filtro Butterworth y envío a memoria.

Fuente: elaboración propia.

La programación en el FPGA se utilizó el ambiente gráfico Labview para FPGA, dentro de los procesos más importantes del FPGA están los determinísticos del ADC de 24 bits para cada uno de los doce canales y la adquisición del tiempo del GPS. Además de las entradas y salidas de información como lo son la medición de temperatura, el despliegue de información en LCD, la grabación de los datos y la comunicación vía Ehternet.

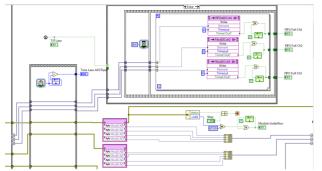

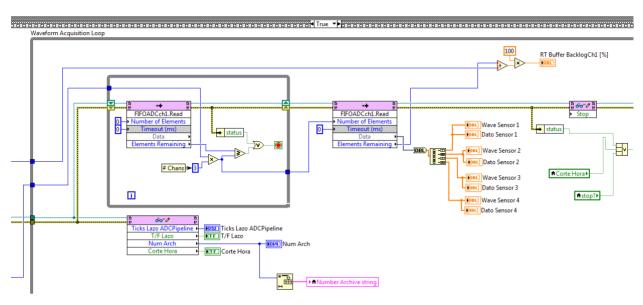

En el FPGA se ejecutan hilos de programación simultáneos para controlar los módulos conectados a las ranuras del chasis. El hilo principal y de ejecución de control determinístico a alta velocidad sirve para la conversión análoga a digital de los doce canales de sensores con señales sísmicas. Para ello se utiliza la técnica pipeline para aumentar el rendimiento del VI y aprovechar las capacidades de procesamiento en paralelo del FPGA de la forma que se muestra en la Figura 4. Primero se configura el número de muestras por segundo del ADC, el mismo que puede ser variable hasta 50ksps. Posteriormente se sincroniza el VI del FPGA con el VI del Real Time para no tener desfases en el tiempo de adquisición de las muestras, posteriormente entra en los lazos con pipeline que cuenta con tres subprocesos internos comunicados entre ellos por shift registers. En este lazo el subproceso principal obtiene las señales acondicionadas de los sensores convertidas a una señal digital de 24 bits por el NI9239. El segundo subproceso es la escritura en memorias FIFO independientes para cada canal con configuración DMA. Y el tercer subproceso es la medición en ticks de reloj del tiempo requerido para la ruta más larga de los tres procesos que es condicionada por las muestras por segundo configuradas para el ADC v la alarma de llenado de la memoria FIFO.

**Figura 4**: Parte del diagrama pipeline para ADC de las 12 señales analógicas.

Fuente: elaboración propia.

El resultado es un bucle con una velocidad de 800 tick de reloj aproximadamente es decir de cumple con la toma de datos del ADC a 50 ksps.

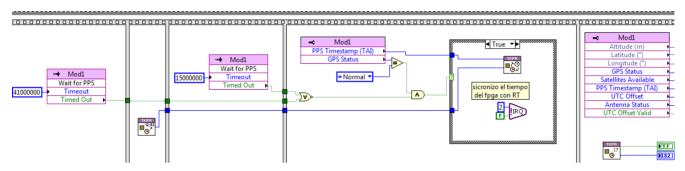

En la Figura 5 se observa la sincronización en tiempo UTC y determinación de la localización de la estación se utiliza el GPS Trimble modelo 66800-40 D con la tarjeta NI 9467 y la librería timekeeper. El lazo dentro del FPGA toma una lectura nueva cada segundo con un desfase máximo de 100 ns. La información se comunica con el Real Time mediante una memoria FIFO y la desincronización de tiempo es guardada en un log para las respetivas correcciones en el procesamiento más exhaustivo de los datos.

Figura 5: Parte del diagrama de programación gráfico para procesamiento continuo del GPS.

Fuente: elaboración propia.

Para finalizar se ejecutan los procesos de baja prioridad como: escritura en el MH-LCD, lectura de voltaje en sistema de alimentación, lectura de temperatura ambiente y parpadeo de led de funcionamiento correcto del equipo. En la Figura 6 se muestra un esquema resumido de los procesos que se desarrollan al interior del FPGA además de las entradas que requiere para su correcto funcionamiento y las salidas que obtenemos en tiempo real.

Figura 6: Esquema de los procesos internos del FPGA.

Fuente: elaboración propia.

# 2.2. Diseño para el Real Time

Para interactuar con el FPGA usamos LabView Real Time, en el cual realizamos la comunicación de datos mediante la lectura de las FIFOS y a la vez realizamos el almacenamiento y procesamiento de datos. Nuestro sistema embebido dentro del real time crea dos lazos determinísticos, el primero para la lectura de los datos de los sensores y el segundo para el tiempo de adquisición de cada muestra.

En primer lugar internamente se produce el proceso de sincronización entre el FPGA y el Real Time y posteriormente se crean diferentes prioridades en los lazos de programación. El lazo de principal prioridad es el de lectura de las memorias FIFO desde el FPGA, las mismas que comunican los datos de las variables de los canales habilitados para el ADC de las señales sísmicas.

En la figura 7 observamos el lenguaje de programación gráfico para la lectura de los datos guardados en las FIFO, se realiza la lectura del número de elementos dentro de la FIFO y fuego la lectura del valor de cada elemento para luego descomponer el array

datos para la gráfica en el host HMI y guardar los datos del ADC en el dispositivo de almacenamiento. En la

de los cuatro primeros canales del ADC y enviar los Figura 8 observamos el esquema del diagrama de datos en ASCII que se guardan en la memoria Flash.

Figura 7: Parte de la programación en el Real time para la lectura de datos de las memorias FIFO.

Fuente: elaboración propia.

Figura 8: Captura del formato de datos guardados en la memoria USB.

HH:MM:SS mes/día/año 137.329102E-3,131.607056E-3,263.214111E-3,53.405762E-3,21:07:04 08/02/2017 -183.105469E-6,-34.332275E-6,190.734863E-6,-188.827515E-6,21:07:04 08/02/2017 -80.108643E-3,-55.313110E-3,-17.166138E-3,-236.511230E-3,21:07:05 08/02/2017 307.083130E-3,362.396240E-3,74.386597E-3,185.012817E-3,21:07:05 08/02/2017

Fuente: elaboración propia.

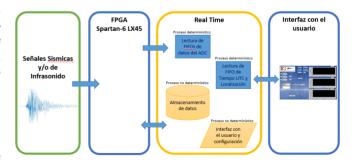

Los datos del ADC son guardados en un archivo ASCII para luego transformarlo a miniseed mediante la librería de IRIS ascii2mseed [19]. Se genera un nuevo archivo por cada cuatro canales de adquisición cada hora, los mismos que son guardados en orden conjuntamente con la especificación del nombre de la estación, ubicación y hora en que fue generando el nuevo archivo. En la Figura 9 observamos un esquema de los procesos que se desarrollan en el procesador en tiempo real y su prioridad clasificada en procesos determinísticos y no determinísticos.

# 2.3. Diseño de la Interfaz de Usuario

Se presenta una interfaz amigable en la que podemos visualizar gráficamente los datos de los sensores conectados al sistema con una presentación de auto escala para mejorar la visualización de los eventos. En la interfaz de usuario es posible visualizar además los datos de temperatura, dirección en donde se grabarán los archivos, escala de las gráficas, estado del GPS, el tiempo UTC, altitud, latitud, longitud, los satélites que están habilitados y los errores producidos. Mediante la interfaz de usuario podemos detener también la adquisición de los datos de la estación si así fuera necesario. En la Figura 10 se muestra la interfaz de usuario que fue desarrollada en conjunto con el personal que realiza el monitoreo de las estaciones sísmicas para que sea de fácil manejo y se ajuste a las necesidades de los usuarios finales.

Figura 9: Esquema de los procesos internos del Real Time.

Fuente: elaboración propia.

Figura 10: Pantalla de Interfaz con el usuario.

Fuente: elaboración propia.

## 2.4. Acondicionamiento de señal del sensor

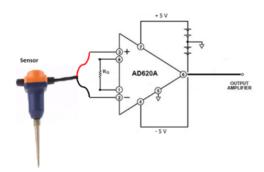

El sistema embebido puede recibir señales de -10 Vdc a +10 Vdc, dependiendo del sensor que se desea conectar al equipo se debe realizar el acondicionamiento apropiado de la señal. Para el presente caso utilizaremos geófonos de la marca Sercel modelo SG-10 con una frecuencia natural de 10Hz [20]. En la Figura 11 se muestra el circuito para el acondicionamiento de señal se utiliza un amplificador de instrumentación AD620 con ganancia de 10 [21].

$$R_G = \frac{49,4k\Omega}{10-1} = 5488,88\tag{1}$$

**Figura 11**: Acondicionamiento de la señal del sensor SG-10.

Fuente: elaboración propia.

# 2.5. Transmisión en tiempo real

Las estaciones sísmicas y volcánicas deben ser instaladas en diversos lugares con una topografía muy compleja lo que dificulta las comunicaciones e incluso el acceso al sitio. Por ello se ve en la necesidad de utilizar redes de comunicación de radio frecuencia en

banda libre de 900 MHZ que además son confiables y de fácil mantenimiento. La trasmisión de los datos sísmicos adquiridos en el digitalizador desde el punto donde es instalada la estación hasta la base de recepción y análisis de datos es trasparente para el usuario final.

Figura 12: Ejemplo de un radioenlace de transmisión de datos hacia el centro de monitoreo de datos [12].

Los equipos utilizados son los radios freewave FGR2-P [23], que tienen un rendimiento superior a 154 kbps sobre el aire y seguridad de cifrado AES para evitar el acceso no autorizado a la información. A continuación en la figura se muestra un esquema de trasmisión de los datos hacia la base del IG (Figura 12).

# 2.6. Estado de Salud de la estación sísmica

Para facilitar el mantenimiento preventivo del equipo se adiciona un sistema para medir el voltaje de alimentación y temperatura ambiente de la estación. Se utiliza una entrada del ADC NI 9239 para tomar el voltaje. Se toma como valor máximo de las baterías de 15 V y se realiza un divisor de voltaje para 3. Se realiza una medición cada 5 minutos y se actualiza en el sistema.

$$V_{out} = \frac{R_1}{R_1 + R_2} V_{in} \qquad si R_2 = 2R_1 \qquad (2)$$

$$V_{inmax} = 15V dc$$

La medición de la temperatura es importante para prolongar la vida útil de los elementos electrónicos. Si se tiene mediciones de temperatura bajas como en nevados o páramos en los mantenimientos se prevea además la colocación de aislamiento térmico de los sensores y equipos más sensibles. O en caso de registro de temperaturas superiores a los 30 °C se prevea en el mantenimiento el cambio de los sistemas de ventilación.

# 3. Resultados

Para validar el funcionamiento correcto del equipo se realizaron una serie de pruebas bajo condiciones de operación que simulen su utilización en estaciones de campo. Las pruebas incluyen precisión, repetitividad, confiabilidad, consumo de energía, operación y manejo de la interfaz de usuario.

## 3.1. Precisión

Mediante el uso un equipo de medición con visualización gráfica se toman varias muestras de captura de las formas de onda de un sensor SG-10 en la interfaz de usuario y se la compara con grafica obtenida en un equipo de medición con visualización gráfica. En la Figura 13 y 14 se muestran los resultados obtenidos, observandose la misma forma de onda en amplitud y tiempo en los dos equipos en mediciones diferentes realizadas bajo las mismas condiciones.

Figura 13: Medición realizada con un sensor SG-10 sin amplificación.

Fuente: elaboración propia.

Figura 14: Medición realizada con un sensor SG-10 con ganancia de amplificación 10.

Fuente: elaboración propia.

# 3.2. Repetitividad

Las mediciones del equipo grabadas en los archivos almacenados de las memorias cumplen con el concepto de repetitividad y reproducibilidad que son requeridos, ya que es de vital importancia que la misma información que es censada sea almacenada para luego poder ser reproducida y realizar estudios geodinámicos.

## 3.3. Confiabilidad

Es un equipo altamente confiable, se ha llevado a cabo pruebas durante periodos de tiempo de ocho días cada uno para verificar que el equipo puede seguir funcionando sin corte en la adquisición y grabación de datos, siendo las pruebas satisfactorias.

# 3.4. Consumo de Energía

Al ser el prototipo un sistema embebido debe cumplir con la característica de bajo consumo de energía. Bajo condiciones normales se llevaron a cabo muestras del consumo en de energía dando como resultado  $4,5~\rm W$  de potencia de consumo y un máximo de  $5~\rm W$  en el arranque de los procesos internos.

# 3.5. Operación y manejo de la interfaz de usuario

Como se muestra en la Figura 15, el prototipo fue instalado en una de las quebradas del Volcán Cotopaxi para probar su operación en campo con resultados positivos y grabación de eventos volcano-tetónicos y lahares. Los resultados de los eventos registrados son parte un trabajo futuro en el que se realizará el procesamiento de las señales sísmicas, como, determinación de la fuente, velocidad de un lahar (flujo de lodo), entre otros.

El conjunto de controles e indicadores que se muestran en la interfaz de usuario son amigables y fáciles de usar. Los usuarios finales realizaron pruebas del software y con una recolección de las sugerencias se obtuvo el interfaz final que se muestra en la Figura 16.

Figura 15: Instalación del prototipo en una de las principales quebradas del Volcán Cotopaxi.

Fuente: elaboración propia.

Figura 16: Interfaz de usuario del Prototipo.

Fuente: elaboración propia.

#### 4. Conclusiones

La opción de tener a disposición un equipo confiable de alta resolución y flexible a adaptarse a una estación multiparamétrica sísmica u vulcanológica con datos acerca del funcionamiento interno de la estación y facilitar los mantenimientos preventivos de las estaciones es productivo para mantener estaciones con una alta disponibilidad la mayor parte del año. Gracias al avance de la tecnología FPGA hemos creado un prototipo de adquisición para aplicaciones geodinámicas robusto, confiable y de una alta precisión. El uso de un FPGA y un procesador nos permiten tener un nivel de confiabilidad superior que al utilizar otras tarjetas tales como arduino, raspberry, etc.

La creación de un prototipo especializado brinda flexibilidad en cuanto a la adaptación a las distintas investigaciones y pruebas. Lo cual es útil para gestionar nuevos conocimientos que integren distintas metologías e hipótesis. Actualmente el sistema se encuentra instalado con un arreglo de sensores para cálculo de la velocidad de paso de lahares en el volcán Cotopaxy y está adquiriendo información 24/7 con una tasa de adquisición de 100-200 muestras por segundo con el objetivo de mitigar los efectos de esta constante amenaza en la población.

El sistema desarrollado está basado en la última tecnología existente (FPGA), que mejora de manera ostensible la capacidad de procesamiento, la velocidad de almacenamiento y el tiempo de respuesta del equipo, lo que nos permite obtener sistemas que trabajan con un rango dinámico superior a los 120 dB. Además el equipo puede manejar con una ranura de ampliación hasta 24 canales para sensores de diferentes tipos con un solo FPGA, lo que actualmente no existe en el mercado. Este equipo es de muy bajo costo, lo que contribuirá a realizar proyectos de investigación en Universidades donde el factor económico es muy importante.

## Referencias

- [1] Geoenciclopedia, "Cinturón de Fuego del Pacífico Información Características Geografía". línea]. 2017.[En Disponible http://www.geoenciclopedia.com/ en: cinturon-de-fuego-del-pacifico/

- [2] BBC Mundo, "¿Por qué el 90% de los terremotos suceden en el Cinturón del Pacífico? BBC Mundo", 2017. [En línea]. Disponible en: http://www.bbc.com/mundo/noticias/2014/08/140826\_ciencia\_cinturon\_fuego\_pacifico\_zona\_mas\_sismica\_mundo\_lv

- [3] Ccpems, .El terremoto del 15 de agosto de 2007 en Perú", 2017, [En línea]. Disponible en: http://www.ccpems.exactas.uba.ar/CDs/CDTierra/contents/4\_desastres/cont/terremoto.htm

- [4] G. Asch, "Seismic Recording Systems", 2017.

[En línea]. Disponible en: http://gfzpublic.gfz-potsdam.de/pubman/item/escidoc:4021:

6/component/escidoc:4022/Chapter\_6\_rev1.pdf

- [5] J Wei, Y Deng, Y Gao, J Yang, J Song, "Design and implementation of embedded video acquisition system based on ARM", Modern Electronics Technique. 2016.pp. 30-34

- [6] G. Herrera, Întroducción a LabVIEW para Sistemas Embebidos", 2017. [En línea]. Disponible en: https://ni.adobeconnect.com/p8v2olyn5vy/

- [7] S. Pedre, "Sistemas Embebidos", Laboratorio de Robótica y Sistemas Embebidos, Departamento de computación FCEN UBA, 2017. [En línea]. Disponible en: http://www-2.dc.uba.ar/ charladeborrachos/presentaciones/charla\_ 2012-10-12.pdf

- [8] D. Pellerin y S. Thibault, "Practical FPGA programming in C". Upper Saddle River, N.J.: Prentice Hall Professional Technical Reference, 2005, pp. 3-9.

- [9] R. Simone, Introducción Práctica a los FPGAs", SASE, 2017. [En línea]. Disponible en: http://www.sase.com.ar/2012/files/2012/ 10/SASE-2012-FPGA.pdf

- [10] J. Teubner y L. Woods, "Data processing on FPGAs". Morgan & Claypool, 2013.

- [11] S. Casco, Raspberry Pi, Arduino y Beaglebone Black Comparación y Aplicaciones", Universidad Católica Nuestra Señora de la Asunción, Facultad de Ciencias y Tecnología, 2017. [En línea]. Disponible

- en: http://jeuazarru.com/wp-content/uploads/

2014/10/MiniPCs.pdf

- [12] Arduino, "Arduino Ethernet", 2017. [En línea]. Disponible en: https://store.arduino.cc/usa/arduino-ethernet-rev3-without-poe

- [13] F. Moya, .Entradas y salidas digitales · Taller de Raspberry Pi", 2017. [En línea]. Disponible en: https://franciscomoya.gitbooks.io/taller-de-raspberry-pi/content/es/elems/gpio.html

- [14] Beagleboard, "BeagleBoard.org black", 2017. [En línea]. Disponible en: https://beagleboard.org/black

- [15] National Instruments, "User manual and specifications, Ni cRIO-9075/9076", 2016. [En línea]. Disponible en: http://sine.ni.com/nips/cds/view/p/lang/es/nid/209758

- [16] Digital, "¿Cuál Sistema Operativo Tiene Mi Controlador en Tiempo Real y Por Qué? - National Instruments", 2017. [En línea]. Disponible en: http://digital.ni.com/public.nsf/allkb/ 556A03ACF10B846C86257CDA006D371D

- [17] National Instruments, "User manual and specifications", Ni cRIO-9467, 2016.

- [18] National Instruments, "User manual and specifications", Ni cRIO-9239, 2016.

- [19] GitHub, 2017, [En línea]. Disponible en: https://github.com/iris-edu/ascii2mseed

- [20] C. Macías, "Diseño de un sistema digital de monitoreo de lahares en tiempo real", 2012. [En línea]. Disponible en: http://bibdigital.epn.edu.ec/bitstream/15000/4860/1/CD-4454.pdf

- [21] Analog Devices, "Low Cost Power Instrumentation Amplifier", AD620, 2011.

- [22] J. Córdova, "Diseño e implementación de un sistema automático de adquisición de datos para medición de la concentración de co2 disuelto en fuentes naturales de agua",2017. [En línea]. Disponible en: http://bibdigital.epn.edu.ec/handle/15000/17251

- [23] Freewave, "900 MHz Wireless Data Radios Ethernet and Serial", 2017. [En línea]. Disponible en: http://www.freewave.com/products/fgr2-plus-series/